3-21

Samsung Electronics

CIRCUIT DESCRIPTION

Repair Manual

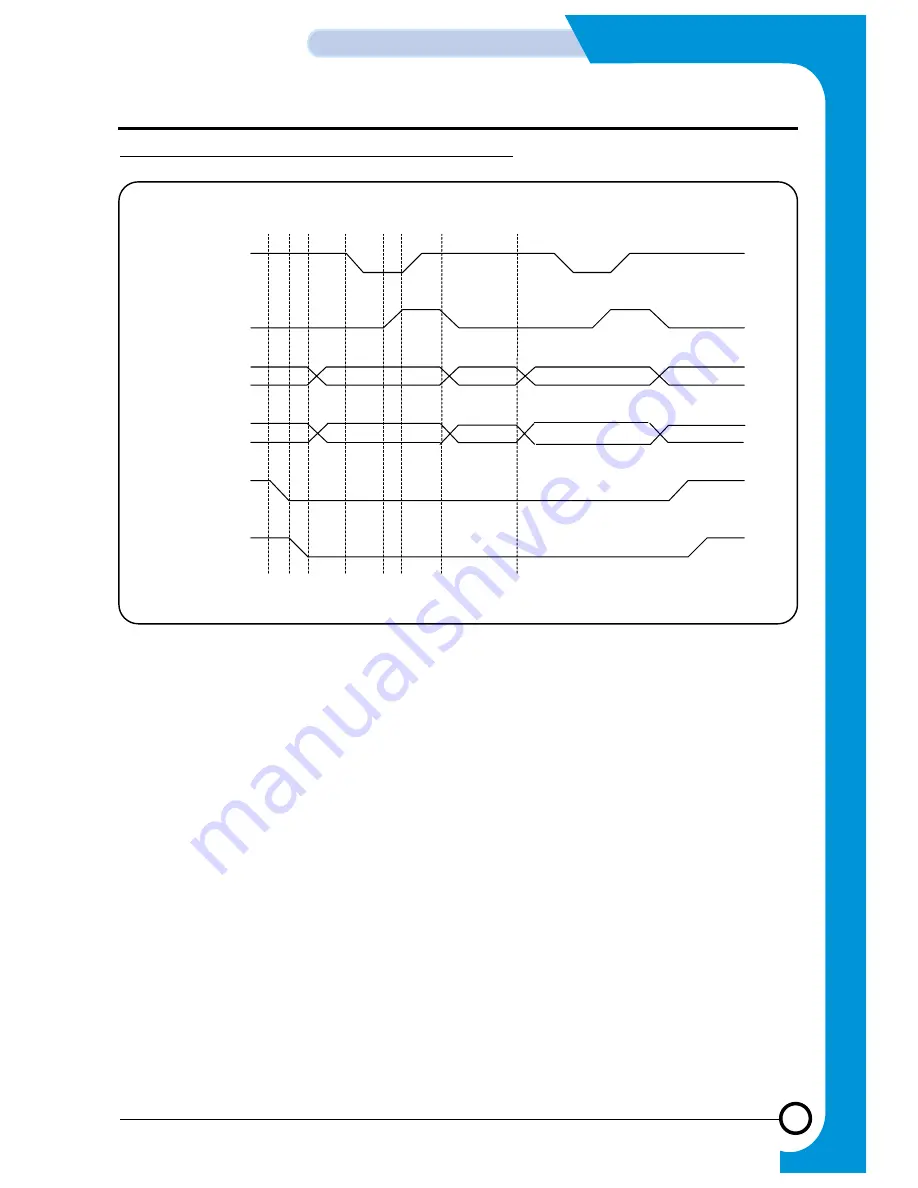

PPD( 7: 0)

BUSY

nACK

nAUTOFD

BYTE0

BYTE1

COMMAND BYTE

DATA BYTE

1 2

3

4

5 6

nINI T

PE

7

8

ECP HARDWARE HANDSHAKING TIMING (REVERSE)

1. The host request a reverse channel transfer by setting nINIT low

2. The peripheral signals that it is OK to proceed by setting PE low

3. The peripheral places data on the data lines and indicates a data cycle by setting BUSY high

4. Peripheral asserts nACK low to indicate valid data

5. Host acknowledges by setting nAUTOFD high

6. Peripheral sets nACK high. This is the edge that should be used to clock the data into the host

7. Host sets nAUTOFD low to indicate that it is ready for the next byte

8. The cycle repeats, but this time it is a command cycle because BUSY is low

Summary of Contents for SF-530 Series

Page 87: ...Electronics ...