AN101

© Kionix 2019 All Rights Reserved

11 July 2019

Page 3 of 27

3.2.

Synchronous Reading (with hardware interrupt)

This example configures and enables the accelerometer to start outputting sensor data with a

synchronous signal (DRDY) and data can read from the output registers.

-

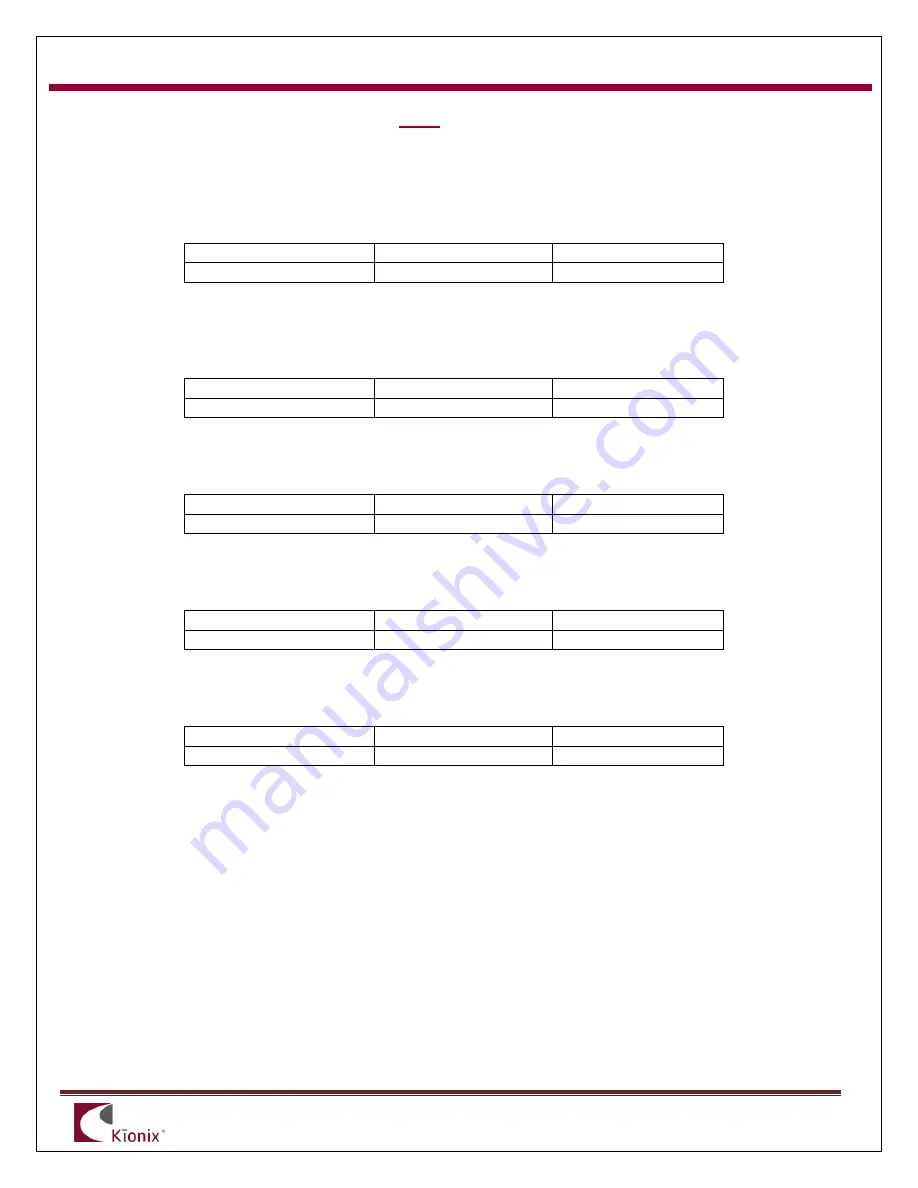

Write 0x00 to Control 1 (CNTL1) to set the accelerometer in stand-by mode

Register Name

Address

Value

CNTL1

0x1B

0x00

-

Write 0x30 to Interrupt Control 1 (INC1) to enable physical interrupt pin INT1, set the polarity

of the physical interrupt to active high and configure for latched operation (Note: if the output

registers are read in a burst sequence, the latched interrupt will auto clear by default).

Register Name

Address

Value

INC1

0x22

0x30

-

Write 0x10 to Interrupt Control 4 (INC4) to set the Data Ready interrupt to be reported on

physical interrupt pin INT1.

Register Name

Address

Value

INC4

0x25

0x10

-

Write 0x06 to Output Data Control (ODCNTL) to set the Output Data Rate (ODR) of the

accelerometer to 50 Hz.

This step is optional as this is also a default setting.

Register Name

Address

Value

ODCNTL

0x21

0x06

-

Write 0xE0 to Control 1 (CNTL1) to set the accelerometer into operating mode (PC1=1), full

power mode (RES=1), data ready enabled (DRDYE=1), range to ±8g (GSEL=0).

Register Name

Address

Value

CNTL1

0x1B

0xE0

-

Acceleration data can now be read from the XOUT_L, XOUT_H, YOUT_L, YOUT_H,

ZOUT_L, and ZOUT_H registers in 2’s complement format synchronously following the rising

edge of INT1.