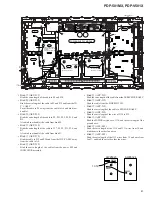

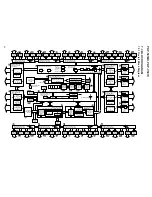

PDP-501MX, PDP-V501X

72

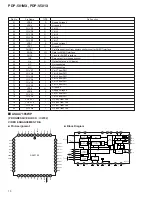

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

N.C.

REG1

INY

REG2

CLPY

INU

SDN

INV

AGND

CLPU

CE

CLP

HREF

CLPV

REG3

DGND

CLK

D7

D6

D5

D4

D3

D2

D1

D0

D'3

D'2

D'1

D'0

V

CCA

V

CCO

V

CCD

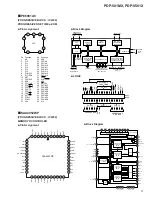

TDA8755T

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

23

24

31

32

V

CCA

V

CCD

V

CCO

AGND DGND SDN

N.C.

REG1

REG2

REG3

D0

D7

HREF

CE

CLK

D'0

D'1

D'2

D'3

V

U

Y

INY

CLPY

CLP

INU

CLPU

CLPV

INV

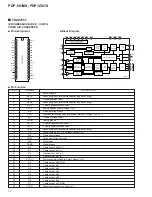

SUPPLY AND REFERENCE

VOLTAGE REGULATOR

CLAMP

LOGIC

CLAMP

V

CLAMP

U

TRACK

AND

HOLD

DIGITAL

MULTIPLEXER

ANALOG

MULTIPLEXER

TRACK

AND

HOLD

TRACK

AND

HOLD

COMPARATOR

128

8-bit

ADC

8-bit

ADC

U AND V

DATA

ENCODER

TTL

I / O

TTL

I / O

TDA8755

TIMING GENERATOR

CLAMP

Y

COMPARATOR

16

TRACK

AND

HOLD

8-bit

PIPELINE

8

8

8

8

8

2

2

2

2

19

20

21

22

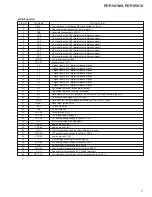

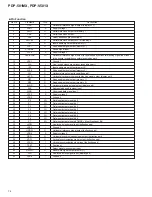

PIN NO.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

PIN NAME

NC

REG1

INY

REG2

CLPY

VCC A

INU

SDN

INV

AGND

CLPU

CLPV

REG3

CE

CLP

HREF

CLK

DGND

D`0

D`1

D`2

D`3

VCC O

D0

D1

D2

D3

D4

D5

D6

D7

VCC D

PIN FUNCTION

Not connected

Decoupling input (internal stabilization loop decoupling)

Y analog voltage input

Decoupling input (internal stabilization loop decoupling)

Y clamp capacitor connection

Analog positive supply voltage (+5V)

U analog voltage input

Stabilizer decoupling node and analog reference voltage (+3.35 V)

V analog voltage input

Analog ground

U clamp capacitor connection

V clamp capacitor connection

Decoupling input (internal stabilization loop decoupling)

Chip enable input(TTL level input active LOW)

Clamp control input

Horizontal reference signal

Clock input

Digital ground

V data output; bit 0(n-1)

V data output; bit 1(n)

U data output; bit 0(n-1)

U data output; bit 1(n)

Positive supply voltage for output stages (+5V)

Y data output; blt 0(LSB)

Y data output; blt 1

Y data output; blt 2

Y data output; blt 3

Y data output; blt 4

Y data output; blt 5

Y data output; blt 6

Y data output; blt 7(MSB)

Digital positive supply voltage (+5V)

7

TDA8755T

(PROGRESSIVE BLOCK : IC4703)

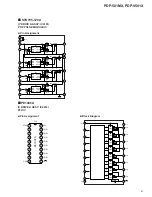

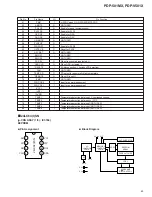

VIDEO A/D CONVERTER

¶

Pin Function

¶

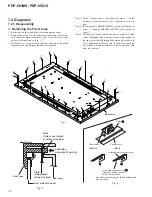

Block Diagram

¶

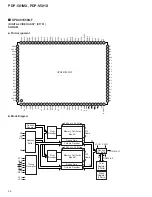

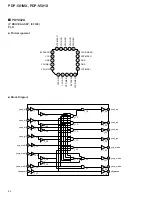

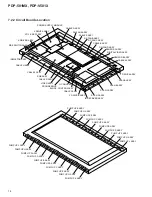

Pin Assignment

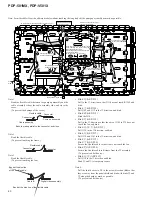

Summary of Contents for PDP-501MX

Page 16: ...PDP 501MX PDP V501X 16 A B C D 1 2 3 4 1 2 3 4 3 3 POWER SUPPLY MODULE 1 2 J 1 2 ...

Page 17: ...PDP 501MX PDP V501X 17 A B C D 5 6 7 8 5 6 7 8 J 1 2 ...

Page 18: ...PDP 501MX PDP V501X 18 A B C D 1 2 3 4 1 2 3 4 3 4 POWER SUPPLY MODULE 2 2 J 2 2 ...

Page 19: ...PDP 501MX PDP V501X 19 A B C D 5 6 7 8 5 6 7 8 J 2 2 ...