PDP-501MX, PDP-V501X

38

6. ADJUSTMENT

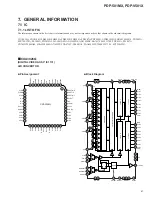

6.1 Adjustments of Parts

Note)

In these adjustments, assembly are indicated by the following

symbols.

A

:ANALOG VIDEO ASSEMBLY

B

:PROGRESSIVE BLOCK

J

:POWER SUPPLY MODULE

G

:Y DRIVE (A) ASSEMBLY

H

:Y DRIVE (B) ASSEMBLY

Note: Position for pasting the drive voltage label

Drive voltage label ARW1077

Adjust so that the output of Pin

2

(R-Y signal) of CN9505 becomes

minimum.

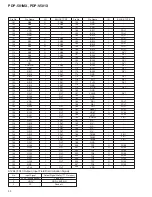

Procedure

Adjusting Item

Input Signal

Adjusting Point

Adjusting Method

1

TINT

Chroma modulation

ramp signal

VR9002

(

A

)

EIA colour bar

EIA colour bar (Colour

saturation 75% only)

EIA colour bar (Colour

saturation 75% only)

B-Y demodulation

angle

Colour (B-Y)

Colour (R-Y)

VR9005

(

A

)

VR9003 (

A

)

VR9004 (

A

)

L4715 (

B

)

Center± 0.2µs

HRA

CLP

9

V

H_A

, V

H_B

voltage

adjustment

100% white signal

V

H A

(Scan IC power supply voltage A)

Check the drive voltage label value at the upper left side of the unit

inside, and adjust RV3302 so that the voltage between Pin

1

(VH_

A) and Pin

4

(GND H_A) of the check connector CN3303 becomes

that value.

V

H B

(Scan IC power supply voltage B)

Check the drive voltage label value at the upper left side of the unit

inside, and adjust VR3301 so that the voltage between Pin

1

(VH_B)

and Pin

4

(GND H_B) of the check connector CN3304 becomes

that value.

VR3302 (

G

)

VR3301 (

H

)

Deflection PLL

adjustment

Acquisition PLL

adjustment

2

3

4

5

6

Adjust so that the output of Pin

4

(B-Y signal) of CN9505 becomes

0.525 Vp-p ±10 mV.

a

b

Any standard

signal

Any standard

signal

Adjust so that the output of Pin

2

of CN9505 becomes 0.525 Vp-p

±10 mV.

Adjust so that the voltage of TP

K4701 becomes 2.6

±

0.1V.

Adjust so that the amplitudes of a and b become equal at the output

of Pin

4

of CN9505.

Adjust the timing of the waveforms of Pin

3

(CLP) of CN4703 and TP

K4702 (HRA) so that the rising edge of the HRA pulse are at the

center of the CLP pulse.

7

VCO free-run

frequency for 910

fH clock

Y/C mode chroma

signal output level

VR3350

(

AP

)

NTSC RAMP signal

(with burst and chroma)

Set the input to "C.VIDEO", observe the voltage of Pin

7

of IC3352

(TP P3350), and adjust so that the voltage becomes 2.5V

±

0.1V using

the digital voltmeter.

Set the input to "S.VIDEO", observe the Q3354 emitter using the

oscilloscope, and adjust so that the level of the chroma signal becomes

400 mV

±

20 mV.

8

VR3351

(

AP

)

NTSC RAMP signal

(S terminal signal with

burst and chroma)

L4706 (

B

)

Summary of Contents for PDP-501MX

Page 16: ...PDP 501MX PDP V501X 16 A B C D 1 2 3 4 1 2 3 4 3 3 POWER SUPPLY MODULE 1 2 J 1 2 ...

Page 17: ...PDP 501MX PDP V501X 17 A B C D 5 6 7 8 5 6 7 8 J 1 2 ...

Page 18: ...PDP 501MX PDP V501X 18 A B C D 1 2 3 4 1 2 3 4 3 4 POWER SUPPLY MODULE 2 2 J 2 2 ...

Page 19: ...PDP 501MX PDP V501X 19 A B C D 5 6 7 8 5 6 7 8 J 2 2 ...