101

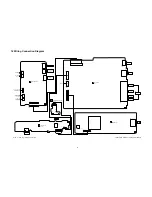

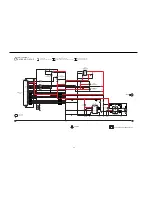

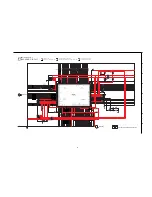

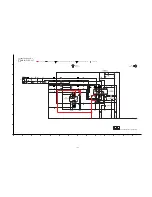

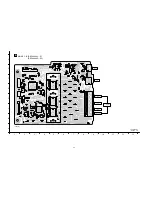

17.3. Main Circuit

A

1

2

3

4

5

6

7

8

9

10

11

12

13

14

C

D

B

E

G

H

F

B

MAIN CIRCUIT

SCHEMATIC DIAGRAM - 7

SA-XH50P/PC MAIN CIRCUIT

3/8

4/8

7/8

2/8

6/8

8/8

1/8

5/8

TO MAIN

CIRCUIT (2/8)

TO MAIN

CIRCUIT (5/8)

P1

: MUSIC PORT/AUX/TUNER AUDIO INPUT SIGNAL LINE

: -B SIGNAL LINE

: +B SIGNAL LINE

: FM SIGNAL LINE

: AUDIO OUTPUT SIGNAL LINE

DGND

AGND

R601

1K

R600

1K

0.1

C605

R605

220

R604

220

R606

1K

R658

2.2K

22P

C602

22P

C601

R611

0

G2

G1

JK600

FM ANT

VA600

EZAEG2A50AX

LB600

J0JBC0000032

C600

1000P

0.1

C606

R602

4.7K

R603

4.7K

R612

0

K301

0

K302

0

L600

G1CR18JA0020

4

12

1

2

14

T1

17

19 18

16

15

20

3

13

THERMAL

PAD

5

11

10

8

9

7

6

VUEALLPT040

FM RADIO RECEIVER

IC600

C604

1

C603

1

X600

H0A327200097

1K

R613

1K

R614

C607

100

C608

0.1

0

R631

R633

0

0

R632

0

R630

TUN_INT

R615

47K

R616

47K

TUN-RCH

TUN-LCH

TUN_SCLK

TUN_SDIO

TUN_REST

R609

47K

R610

47K

C136

50V3.3

RST

SEN

NC

RFGND

FMI

NC

AMI

GND

ROUT

RCLK

VIO

VDD

SCLK

SDIO

DFS

DCLK

GCGPO2

LOUT

DOUT

GCGPO1

8200P

C609

8200P

C610

PW_3.3VREF

6

8

9

7

2

1

4

5

3

10

CN202

TO uP DOWNLOADER

SYS5VGND

PW_SYS6V

0.01

C205

1

D201

B0BC7R5A0263

LB201

0

LB200

0

C214

1

1

4

2

3

C0DBGYY00887

+3.3V REGULATOR

IC202

RESET

CE

VOUT

VDD

GND

CE

CE

DGND

EPM

EPM

RESET

TXD

TXD

CNVSS

CNVSS

BUSY

BUSY

CLOCK

CLOCK

VREF

RXD

RXD

C219

Summary of Contents for SA-XH50P

Page 13: ...13 4 1 Others Licences ...

Page 16: ...16 5 4 Speaker Connection ...

Page 17: ...17 5 5 Linked Operations with the TV VIERA LINK HDAVI Control ...

Page 18: ...18 ...

Page 19: ...19 5 6 Connection with an ARC compatible TV ...

Page 21: ...21 5 7 2 File Extension Type Support MP3 JPEG ...

Page 23: ...23 3 Gently pull out the tray 4 Remove disc ...

Page 46: ...46 10 2 Main Components and P C B Locations ...

Page 82: ...82 ...

Page 92: ...92 ...

Page 94: ...94 ...