MeiG

Product

Manual

of

SLM750

Module

SLM750

Module

Hardware

Design

Page 39, total 84 pages

3.8.1 Hardware reset

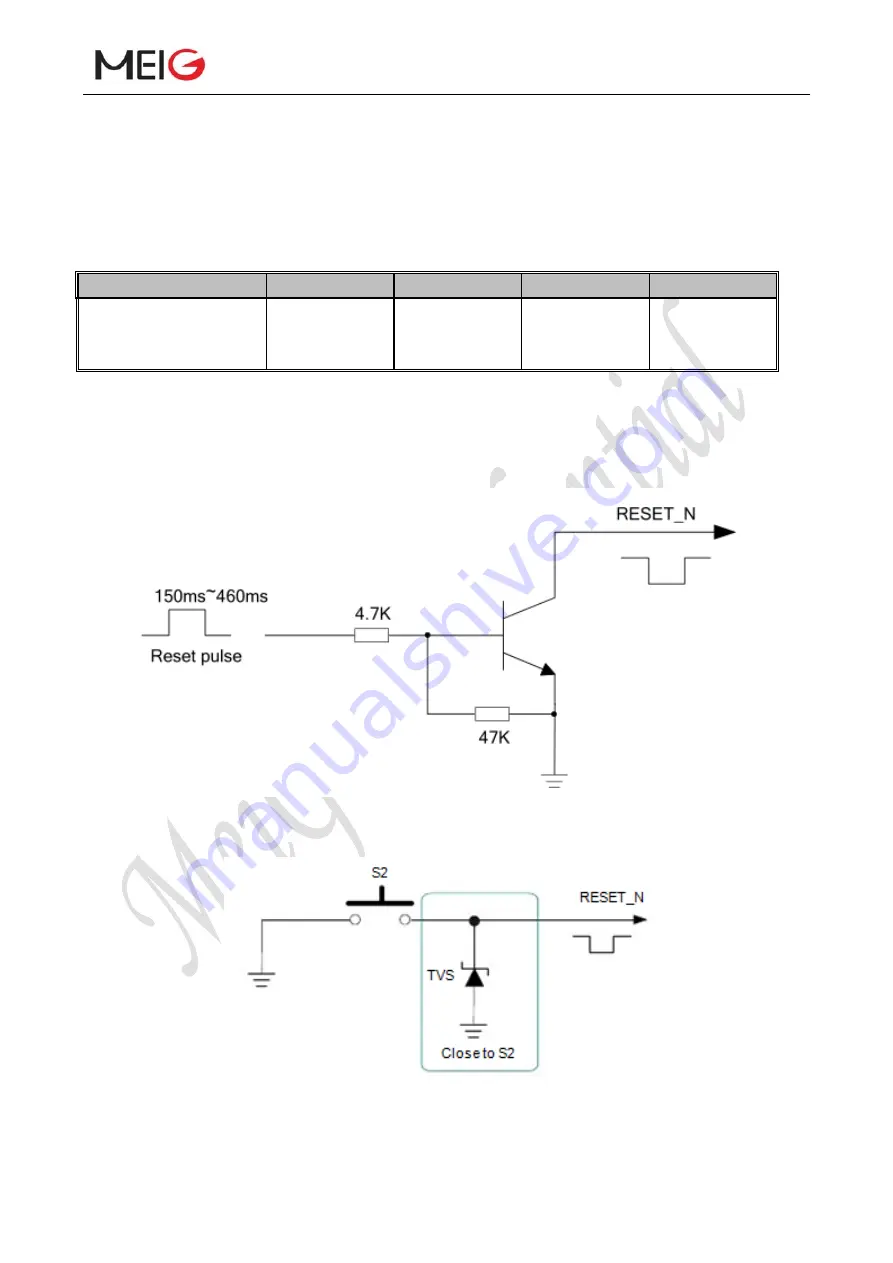

When the module is in operation, puling down 150~460ms of the RESET_N pin to reset

module. The RESET_N signal is sensitive to interference.

Table 8: RESET_N pin description

Pin name

Pin number

Function

DC features

Description

RESET_N 20

Reset

module

V

IH

max=2.1V

V

IH

min=1.3V

V

IL

max=0.5V

Reference circuit is as follows: you can use open set driver circuit or button to control

RESET_N pin.

Figure 11 Reference circuit of RESET_N by using driving circuit

Figure 12 Reference circuit of RESET_N by using button

The reset timing figure is as follows: