ECP5 and ECP5-5G High-Speed I/O Interface

Technical Note

© 2014-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

FPGA-TN-02035-1.3

39

DQSR 90

D

Q 0

Q 1

RST

SCLK

RDPNTR[2:0]

WRPNTR[2:0]

IDDRX2DQA

DQSR90

D

RST

SCLK

RDPNTR[2:0]

WRPNTR[2:0]

CLK

RST

UDDCNTLN

FREEZE

DDRDEL

LOCK

DDRDLLA

DCNTL[7:0]

Sclk

From DELAG

output of dq _7

Dcntl [7:0]

dq _0

.

.

.

.

datain _0(0)

ECLK

ECLK

Q 2

Q 3

datain _0(8)

datain_0(16)

datain _0(24)

Q 0

Q 1

datain _0(7)

Q 2

Q 3

datain _0(15)

datain _0(23)

datain _0(31)

Refclk

ECLKI

STOP

ECLKO

EHXPLLL

CLKOP

CLKI

RST

LOCK

Lock

ECLKSYNCB

CLKDIVF

CLKI

RST

ALIGNWD

CDIVX

1'b0

DQSBUFM

DQSI

DQSR 90

DDRDEL

READ[1:0]

WRPNTR[2:0]

RDPNTR[2:0]

SCLK

RST

READCLKSEL0

READCLKSEL1

READCLKSEL2

DQSW270

RDLOADN

RDMOVE

RDDIRECTION

WRLOADN

WRMOVE

WRDIRECTION

DATAVALID

BURSTDET

RDCFLAG

WRCFLAG

ECLK

DYNDELAY[7:0]

DQSW

QWL

QWL

dq_0_wl

dq_7_wl

PAUSE

Eclk

DELAYG

DEL _MODE =

DQS _ALIGNED _X 2

DLL_LOCK

FREEZE

UDDCNTLN

DLL_RESET

DDR_RESET

STOP

START_CLK

RST

UPDATE

READY

MEM_SYNC

Sync_clk

sync_reset

Update

Ready

Pll _Reset

Pause_sync

PAUSE

pause_data

(To

output

side)

dqs_0

read_0[1:0]

readclksel0_0

readclksel1_0

readclksel2_0

dyndelay[7:0]

rdloadn_0

rdmove_0

rddirection_0

wrloadn_0

wrmove_0

wrdirection_0

rdcflag_0

wrcflag_0

datavalid_0

burstdet_0

IDDRX2DQA

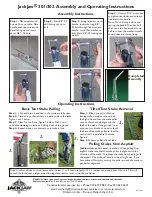

Figure 6.8. DDR2, DDR3/DDR3L, LPDDR2, and LPDDR3 Read Side Implementation

The read side is implemented using the following software elements.

DDRX2DQA element to capture the data

DDRDLLA is used to generate the delay code for DQSBUFM to get the 90° phase shift on the DQS input (DQSR90).

The incoming DQS clock (DQSI) is routed through the DQSBUFM module to the DQS clock tree.

The DQSBUFM receives the delay code from DDRDLLA and generates the delayed DQS signal to IDDRX2DQA.

The DQSBUFM is used to generate the Read and Write pointers that is used to transfer data from the DQS to ECLK

inside the IDDRX2DQA module.

Read 1, 0 and Readclksel_2, 1, 0 signals of DQSBUFM are used by the user logic to obtain the optimal READ pulse

position and driven by the user logic to generate a clean DQS output signal based on the trained READ pulse with

respect to preamble and postamble.

The dynamic delay control ports are available on the DQSBUFM module when you select the enable

dynamic

margin control

option.

DYNDELAY[7:0] of DQSBUFM is used to perform write leveling. If write leveling is not used, it is connected to 0.

Port QWL of IDDRX2DQA is used for DDR3/DDR3L and LPDDR3 to support write leveling. It is used to deliver the

write leveling monitor signals from the memory device to the FPGA user logic.

MEM_SYNC soft IP must always be included in the interface. It is required to avoid issues on DDR memory bus and

update code in operation without interrupting interface operation. When a DDR memory interface IP is generated

from Clarity Designer, the MEM_SYNC soft IP block is also generated and included.