ECP5 and ECP5-5G High-Speed I/O Interface

Technical Note

© 2014-2020 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at

All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

34

FPGA-TN-02035-1.3

6.2.

Features for Memory Interface Implementation

The ECP5 and ECP5-5G devices contain a variety of features to simplify implementation of the read and write

operations of a DDR interface:

DQS Clock Tree spanning the DQS group

DDRDLL used to generate the 90° delay codes

DLL-compensated DQS delay elements

Input FIFO for read data clock domain transfer

Dedicated DDR Memory input and output registers

Dynamic Margin Control Circuit to adjust Read and Write delays

Input/Output Data Delay used to compensate for DQS clock tree delay

6.2.1.

DQS Grouping

In DDR interfaces with eight DQ pads associated to one DQS pad, each DQS group generally consists of at least 10 I/O

(one DQS, eight DQ, and one DM) for an 8-bit DDR2 memory interface or 11 I/O (two DQS, eight DQ, one DM) to

implement a complete 8-bit DDR3/DDR3L/LPDDR2/LPDDR3 memory interface. In case of LPDDR2/3, two additional

DQS groups are required to generate the CA[9:0] (with 10 I/O) and Control/CLKP/CLKN (with 5 I/O for LPDDR3 and 4 I/O

on LPDDR2) outputs.

In ECP5 and ECP5-5G devices, a DQS group consists of 12 to 16 I/O depending on the device and package selected to

accommodate these DDR interface needs. ECP5 and ECP5-5G devices support DQS signals on the left and right sides of

the device.

Each DQS signal spans across 12 to 16 I/O. Any 10 (for DDR2) or 11 (for DDR2/DDR3/LPDDR2/LPDDR3) of these 16 I/O

spanned by the DQS can be used to implement an 8-bit data side interface. For LPDDR2/LPDDR23, any group with ten

I/O is required for CA[9:0] bus and another group with five I/O for LPDDR3 and four I/O for LPDDR2 is required to

generate the Control and CLKP/CLKN outputs. In addition to the DQS grouping, you must also assign the reference

voltage (VREF) input to an I/O in that bank required to implement the referenced I/O standard.

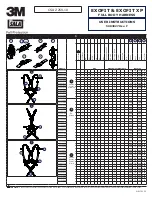

DQS PAD (10

th

pad)

16 I/ O PADS

DQ , DM

DQ , DM

- -

- - - -

DQS# PAD (11

th

pad)

Figure 6.5. DQ-DQS Grouping

shows a typical DQ-DQS group for ECP5 and ECP5-5G devices. The 10th I/O Pad of this 16 I/O group is the

dedicated DQS pin. All the nine pads before the DQS and six pads after the DQS are covered by this DQS bus span. If a

differential DQS pair is required, then the 11th pad is used by the DQS# signal. You can assign any other I/O pads to be

DQ data or DM pins. Therefore, for example, to implement a 32-bit wide memory interface you would need to use four

such DQ-DQS groups when eight-to-one DQ-DQS association is used.

In case of LPDDR2 and LPDDR2, two additional DQS groups are required to assign the CA[9:0] and the control signals.

In case of DDR2/DDR3/DDR3L, additional I/O pads are required to implement address, command, and control. They do

not have to be I/O in DQS groups but need to use 1x gearing generic output DDR capable pads.

Each of the dedicated DQS pins is internally connected to the DQS phase shift circuitry. The pin out sheets included as

part of

ECP5 and ECP5-5G Family Data Sheet (FPGA-DS-02012)

shows pin locations for each of the DQS groups.