Lake Shore Model 642 Electromagnet Power Supply User’s Manual

5-10

Computer Interface Operation

5.1.4.3

Error Status Register Sets

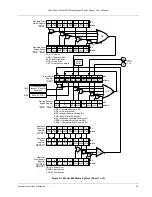

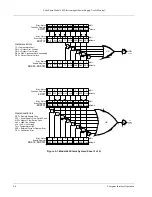

As shown in Figure 5-1, there are two register sets in the error status system of the Model 642; Hardware Error Status

Register, and Operational Error Status Register.

5.1.4.3.1

Hardware Error Status Register Set

The Hardware Error Status Register reports the following instrument hardware error events: temperature fault, output

over voltage, output over current, DAC processor not responding and output control failure. Any or all of these events

may be reported in the standard event summary bit through the enable register, see Figure 5-4. The Hardware Error

Status Register is the first value of the two values associated with the Error Status Registers. The Error Status Enable

command (ERSTE) programs the enable register and the query command (ERSTE?) reads it. ERSTR? reads and clears

the Error Status Register. The used bits of the Error Status Event Register are described as follows:

Temperature Fault (TF), Bit (4)

– This bit is set if the internal temperature of the instrument exceeded the maximum

safe value of 45

°C. The instrument will shut down within 10 seconds of detecting this fault.

Output Over Voltage (OOV), Bit (3)

– This bit is set if the output voltage exceeded the compliance voltage limit

setting.

Output Over Current (OOC), Bit (2)

– This bit is set if the output current is above 62 A exceeding the maximum

output current of the instrument.

DAC Processor Not Responding (DAC), Bit (1)

– This bit is set to indicate that communication to the DAC processor

has failed.

Output Control Failure (OCF), Bit (0)

– This bit is set if there is a failure on the output control board.

To Bit 2 (HESB) of

(See Figure 5-1.)

Status Byte Register

Not

Not

Event Register

Not

Used

5

Used

Not

Used

Used

ERSTE, ERSTE?

Error Status

Enable Register

Not

7

6

Not

ERSTR?

Used

Used

Name

TF

AND

AND

4

2

3

0

1

Bit

AND

AND

AND

TF

Name

OR

5

5

Used

Not

6

7

Condition Register

Error Status

ERST?

7

6

Not

Used

Used

Not

Error Status

Bit

1

0

3

2

4

OOV

4

3

2

DAC

TF

OCF

1

0

Bit

OOC

Name

OOV

DAC OCF

OOC

OOV

DAC OCF

OOC

Figure 5-4. Hardware Error Status Register