1

2

3

5

4

A

B

C

D

E

F

G

H

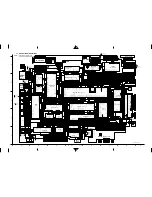

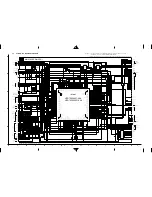

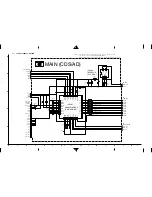

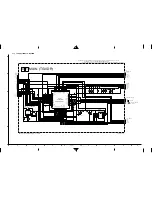

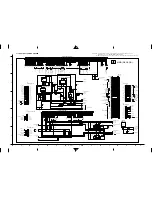

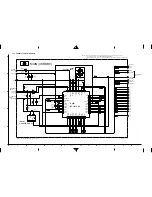

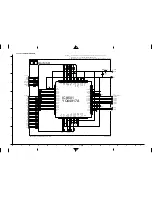

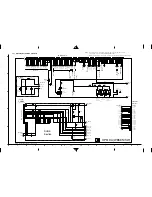

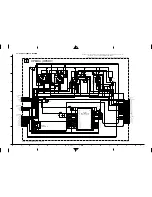

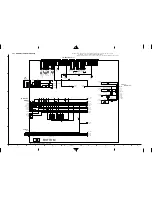

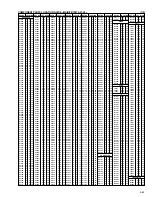

CAM.DSP SCHEMATIC DIAGRAM

4.11

4-24

4-23

IC4301

R4318

GATEPULS

TL4319

TL4320

TL4321

TL4322

HD_SEL

R4321

TL4323

TL4324

TL4325

TL4326

R4320

R4323

R4322

TL4317

TL4318

R4304

ADIN9

ADIN8

ADIN7

ADIN6

ADIN5

ADIN4

ADIN3

ADIN2

ADIN1

ADIN0

BUS15

BUS14

BUS13

BUS12

BUS11

BUS10

BUS9

BUS8

BUS7

BUS6

BUS5

BUS4

BUS3

BUS2

BUS1

BUS0

CDSTB

CRWSEL

CALE

MFLD

MVD

OMT

DSP_RST

CAM_VD

IRIS_PWM

CLK4M5

IRIS_C

C4313

R4303

TL4316

R4307

R4306

RA4307

RA4308

RA4301

RA4302

RA4303

RA4304

RA4305

RA4306

DYO0

DYO1

DYO2

DYO3

DCO0

DCO1

DCO2

DCO3

INH

INV

CLK9A

CLK27A

S_SHUT

OUTV

OUTH

DCI3

DCI2

DCI1

DCI0

DYI3

DYI2

DYI1

DYI0

OUT_VS

OUT_HS

OUT_C3

OUT_C2

OUT_C1

OUT_C0

OUT_Y3

OUT_Y2

OUT_Y1

OUT_Y0

TBCCTL

R4313

R4312

R4311

R4310

R4309

TCMK

TMS

TRST

TDA

TDB

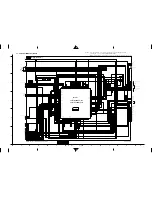

IC4302

REG_3V

C4310

C4302

C4301

REG_1.8V

IC4303

GND

C4306

C4309

C4304

C4305

C4318

C4311

C4312

L4301

L4302

L4303

C4308

DSYIO7

DSYIO6

C4303

C4307

DSYIO5

DSYIO4

DSYIO3

DSYIO2

DSYIO1

DSYIO0

DSCIO7

DSCIO6

DSCIO5

DSCIO4

DSCIO3

DSCIO2

DSCIO1

DSCIO0

CLKDSC

HDDSC

VDDSC

FLDDSC

DSYO7

DSYO6

DSYO5

DSYO4

DSYO3

DSYO2

DSYO1

DSYO0

DSCO7

DSCO6

DSCO5

DSCO4

DSCO3

DSCO2

DSCO1

DSCO0

R4305

TL4315

TL4314

TL4313

TL4312

TL4311

TL4310

TL4309

TL4308

TL4306

TL4305

TL4304

R4317

R4316

TG_36M

HDIN

VDIN

PBLK

CPOB

L4304

C4316

X4301

R4301

R4308

CLK27B

REG_2.5V

C4317

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

22

0.01

22

22

560

10

10

100

100

100

100

10

10

100

100

100

100

100

0.1

10

1

10

0.1

0.01

1

0.1

0.1

0.1

10

10

10

22

1

330

1k

0.1

VSS

VSS

VDDS

CLK45

PWM

VDMDA

MDRV

SDRV

VSS

VSS

VDDS

CLR

OMT

FRP

FLDCPU

VDCPU

HDCPU

CS

AS

RE

WE

BUS0

BUS1

BUS2

BUS3

BUS4

BUS5

BUS6

BUS7

BUS8

BUS9

BUS10

BUS11

BUS12

BUS13

BUS14

BUS15

VSS

VSS

VDDS

ADIN0

ADIN1

ADIN2

ADIN4

ADIN3

ADIN5

ADIN6

ADIN7

ADIN8

ADIN9

CLK36I

HDTG

VDTG

PBLK

OBCP

V

GND[0]

VEXT1[0]

V

GND[6]

VEXT2[0]

VSS

VDDC

FLDDSC

VDDSC

HDDSC

CLKDSC

DSCIO7

DSCIO6

DSCIO5

DSCIO4

DSCIO3

DSCIO2

DSCIO1

DSCIO0

DSYIO7

DSYIO6

DSYIO5

DSYIO4

DSYIO3

DSYIO2

DSYIO1

DSYIO0

V

GND[1]

VEXT1[1]

V

GND[7]

VEXT2[1]

VSS

VDDC

DSCO7

DSCO6

DSCO5

DSCO4

DSCO3

DSCO2

DSCO1

DSCO0

DSY

O7

DSY

O6

DSY

O5

DSY

O4

DSY

O3

DSY

O2

DSY

O1

DSY

O0

V

GND[2]

VEXT1[2]

VSS

VDDC

VSS

VDDC

VEXT1[3]

VGND[3]

NC

NC

CLK27AO

CLK27BO

INVA

INHA

ACO3

ACO2

ACO1

ACO0

AYO3

AYO2

AYO1

AYO0

VSS

VDDC

VGND[8]

VEXT2[2]

VGND[4]

VEXT1[4]

NC

OUTV

OUTH

DCI3

DCI2

DCI1

DCI0

DYI3

DYI2

DYI1

DYI0

INV

INH

DCO3

DCO2

DCO1

DCO0

DYO3

DYO2

DYO1

DYO0

VSS

VDDC

VGND[9]

VEXT2[3]

VGND[5]

VEXT1[5]

KO

VSS

VSS

VSS

VDDC

VDDS

TDO

TDI

TRST

TMS

TCK

VSS

VSS

VSS

VDDC

VDDS

DSVPL

DSVBB

DSVBL

DSVPP

D

V

BGR

D

VBB

DV

B

L

DV

P

L

D

VPP

DMEB

DV

M

SMODE

TCLK

TSEL2

TSEL1

TSEL0

JTEST7

JTEST6

JTETS5

JTEST4

JTEST3

JTEST2

JTEST1

JTEST0

VSS

VSS

VSS

VDDC

VDDS

CKSEL

USEL

TVSEL

VSS

VSS

VSS

VDDS

LP

AG

S

A

V

SSP

A

VDDP

BP

NDRST

CLK72O

CLK54I

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

CLK9AO

CLK9BO

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

ANACTL

NC

NC

NC

NC

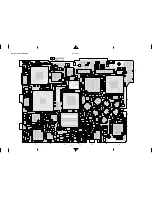

JCY0160-2

NRZ0034-100W

NRZ0034-100W

NRZ0034-101W

NRZ0034-101W NRZ0034-101W

NRZ0034-101W

NRZ0034-100W

NRZ0034-100W

VDD

GND

EC

CE

Vout

R1160N151B-X

/6.3

NOISE

GND

CONT

Vin

Vout

TAR5S25-X

/6.3

NQR0129-002X

NQR0129-002X

NQR0129-002X

/6.3

/6.3

/6.3

NQR0129-002X

NC

GND

OUT

VDD

NAX0319-001X

T

T

T

T

T

#

#

TO

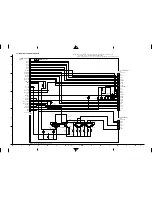

SYSCON-CPU

TO CDS/AD

[CAMERA_DSP]

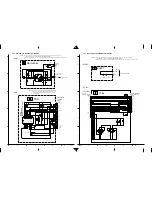

[1.5V_REG]

[1.5V]

[2.5V]

[54MHz_CXO]

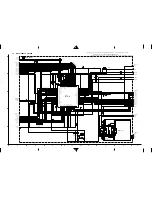

TO MAIN AUDIO

TO VIDEO I/O, DSC

[L:NT

,H:P

AL]

[L:NEC

,H:P

ana]

[L:54,H:108]

TO REGCON

CN114

TO DV MAIN,

VIDEO I/O

[2.5V_REG]

NTSC

PAL

∗

∗

0R0

0R0

R4316

R4317

0 1 MAIN (CAM.DSP)

TO TG/VDR

TO REGCON CN110

TO

REGCON

CN110

TO SERVO,

REGCON CN110

TO REGCON

CN110

TO VIDEO I/O

TO DV MAIN

TO SYSCON-CPU, DV MAIN

TO DV MAIN

TO DV MAIN,

PRE/REC

TO REG

TO DSC

y10280001a_rev0

NOTE : The parts with marked (

∗

) is not used.

# Exchange parts list

When ordering parts, be sure to order according to the Part Number indicated in the Parts List.

For the destination of each signal and further line connections that are cut off from

this diagram, refer to "4.1 BOARD INTERCONNECTIONS".

NOTES :