3. Configuration

35

Cuttable Trace Options and Locations

The ZT 5504 contains several cuttable traces (zero

Ω

shorting resistors) that allow the user to

configure certain options not configurable through the BIOS Setup Utility. The "

Cuttable Trace

Locations

" figure shows the placement of the ZT 5504's cuttable traces. The "

Cuttable Trace

Locations

" table provides a quick cross-reference for the cuttable trace descriptions that follow.

There are two types of cuttable traces on the ZT 5504: single-option and double-option.

Single

option cuttable traces

are implemented using 0603 surface mount pads. A zero

Ω

shorting

resistor is then soldered between these pads to make the connection.

Double option cuttable

traces

(CTx, CTy, CTz) are implemented using three 0603 size surface mount pads. The

zero

Ω

shorting resistor is then soldered between one set of pads, depending on the chosen

option.

CAUTION:

The ZT 5504 has additional cuttable traces not documented in this manual.

These should not be modified by the user. Modifications to documented cuttable traces

should only be performed by a qualified technician familiar with surface mount soldering

techniques. The product warranty is voided if the board is damaged by customer

modifications.

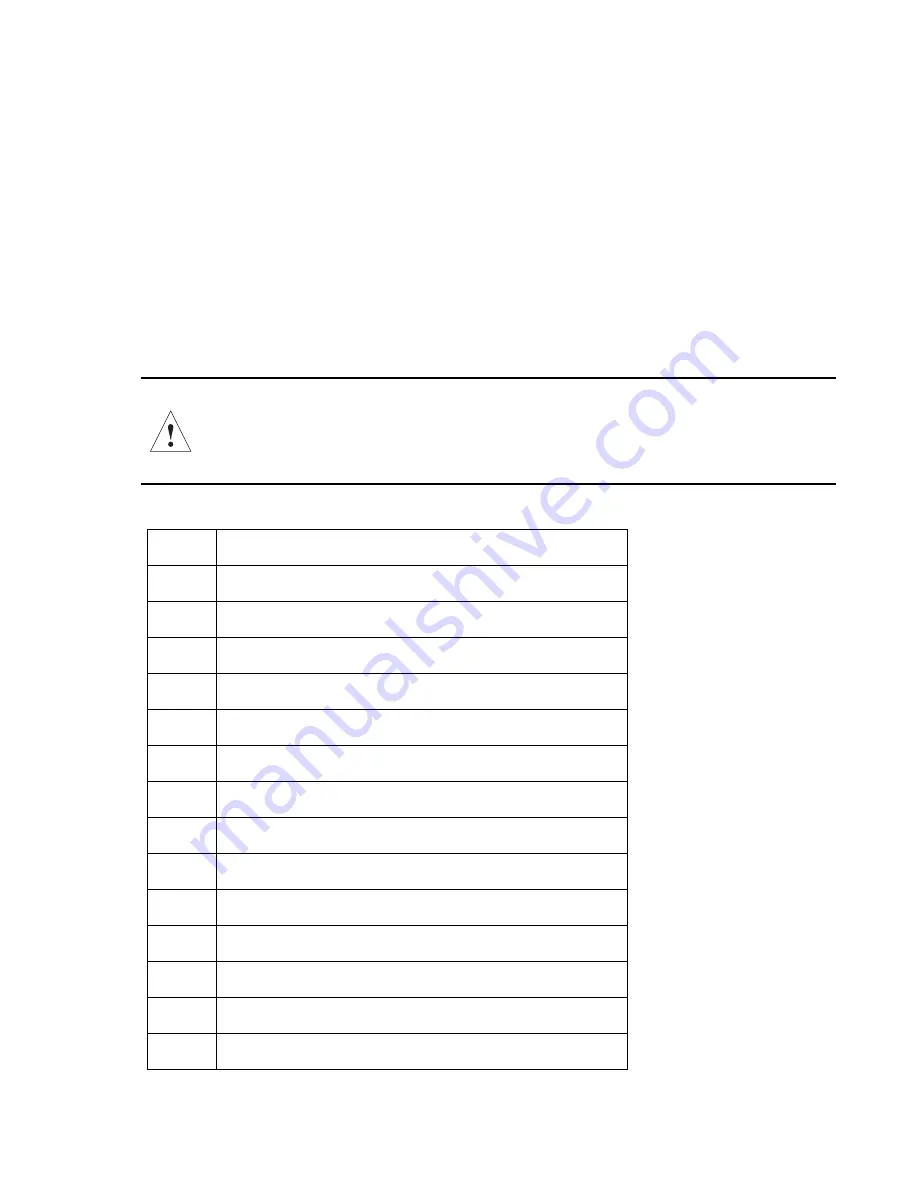

Cuttable Trace Definitions

CT# Description

CT15

USB0 (J8) chassis GND to logic GND

CT16

Revision ID bit 0

CT17

Left ejector chassis GND to logic GND

CT18

COM1 (J10) chassis GND to logic GND

CT19

VGA (J6) chassis GND to logic GND

CT21

Ethernet A (JA4) chassis GND to logic GND

CT22

USB1 (J9) chassis GND to logic GND

CT23

Right ejector chassis GND to logic GND

CT24

Ethernet B (J17) chassis GND to logic GND

CT27

Revision ID bit 3

CT28

Revision ID bit 2

CT29

Revision ID bit 1

CT31

USB1- front or rear routing

CT32

USB1+ front or rear routing

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com