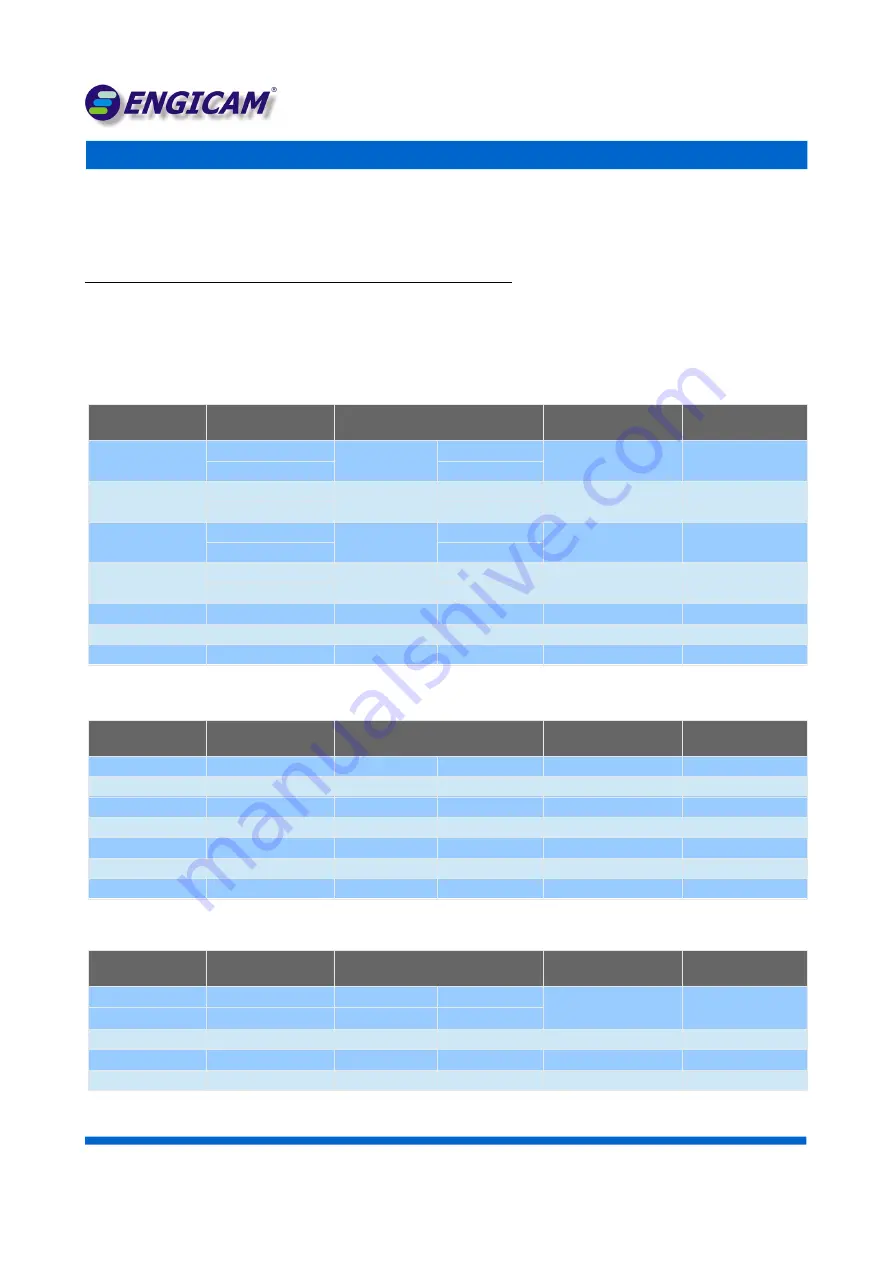

6.1 Peripheral multiplexing description

Following we describe opportunity to use alternative interfaces using the properties of multiplexing pin.

Refer to the NXP's reference manual and documentation for further details.

6.1.1 SPI Interfaces

Using pin multiplexing 's features we may have the following SPI and IIS connections. The tables below show the output signals on the

Connector's module.

ECSPI1 signals interfaces

Pin on connector A

Pin on connector B

Pin Name on i.MX

MicroGEA Signal

reference

Voltage reference

-

47

-

LCD_DAT22

MOSI

+3,3V

72

CSI_DATA0

-

51

-

LCD_DAT23

MISO

+3,3V

74

-

1

-

LCD_DAT20

SCLK

+3,3V

68

CSI_DATA04

-

3

-

LCD_DAT21

SS0

+3,3V

70

CSI_DATA05

-

30

-

LCD_DAT05

SS1

+3,3V

-

28

-

LCD_DAT06

SS2

+3,3V

-

36

-

LCD_DAT07

SS3

+3,3V

Table 23

ECSPI2 signals interfaces

Pin on connector A

Pin on connector B

Pin Name on i.MX

MicroGEA Signal

reference

Voltage reference

75

83

UART5_TX_DATA

CSI_DATA02

MOSI

+3,3V

73

81

UART5_RX_DATA

CSI_DATA03

MISO

+3,3V

7

79

UART4_TX_DATA

CSI_DATA00

SCLK

+3,3V

9

77

UART4_RX_DATA

CSI_DATA01

SS0

+3,3V

-

38

-

LCD_HSYNC

SS1

+3,3V

-

40

-

LCD_VSYNC

SS2

+3,3V

-

61

-

LCD_RESET

SS3

+3,3V

Table 24

ECSPI3 signals interfaces

Pin on connector A

Pin on connector B

Pin Name on i.MX

MicroGEA Signal

reference

Voltage reference

71

-

UART2_CTS_B

-

MOSI

+3,3V

-

59

-

NAND_CE1

69

-

UART2_RTS_B

-

MISO

+3,3V

65

-

UART2_RX_DATA

-

SCLK

+3,3V

67

-

UART2_TX_DATA

-

SS0

+3,3V

Table 25

D N :

4 4