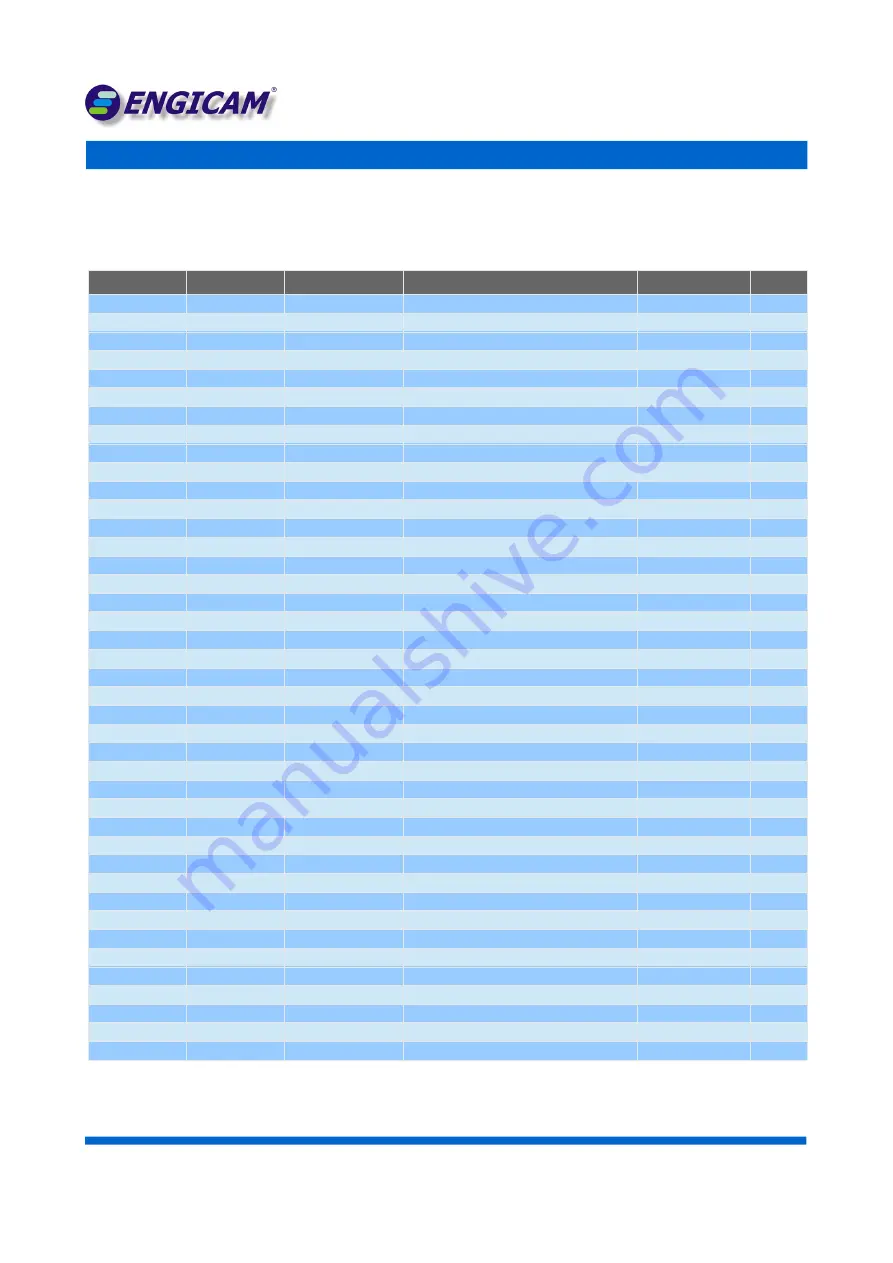

5.10 EPD Interface

The following map represent the EPD connection.

EPD peripheral is available only for parts equipped with Y7 processors

A Connector

B Connector

Name

Primary Function Description

CPU Pin Name Voltage

9

-

EPDC_PWRCTRL01

Panel power control (sw controlled)

UART4_RX_DATA

+3,3V

52

-

EPDC_SDOEZ

Source driver output enable to zero

ENET1_RX_ER

+3,3V

73

-

EPDC_PWRCTRL03

Panel power control (sw controlled)

UART5_RX_DATA

+3,3V

75

-

EPDC_PWRCTRL02

Panel power control (sw controlled)

UART5_TX_DATA

+3,3V

-

1

EPDC_VCOM01

Panel VCOM

LCD_DAT20

+3,3V

-

2

EPDC_PWRCOM

Panel power control (sw controlled)

LCD_DAT10

+3,3V

-

4

EPDC_GDRL

Gate drive-shift direction

LCD_DAT15

+3,3V

-

6

EPDC_PWRSTAT

Panel power good state

LCD_DAT11

+3,3V

-

8

EPDC_PWRCTRL00

Panel power control (sw controlled)

LCD_DAT12

+3,3V

-

12

EPDC_SDSHR

Source driver shift dir

LCD_DAT14

+3,3V

-

14

EPDC_PWRWAKE

Panel power control wakw signal (sw controlled)

LCD_DAT09

+3,3V

-

20

EPDC_PWRIRQ

Panel power IRQ

LCD_DAT08

+3,3V

-

32

EPDC_GDCLK

gate drive clk

LCD_DAT16

+3,3V

-

34

EPDC_GDSP

gate drive start pulse

LCD_DAT17

+3,3V

-

38

EPDC_SDOE

Gate driver output enable

LCD_HSYNC

+3,3V

-

42

EPDC_SDLE

Source driver latch enable

LCD_ENABLE

+3,3V

-

44

EPDC_SDCLK

Source driver shift clk

LCD_CLK

+3,3V

-

49

EPDC_VCOM00

Panel VCOM

LCD_DAT19

+3,3V

-

61

EPDC_GDOE

gate driver output enable

LCD_RESET

+3,3V

-

10

EPDC_BDR00

Panel border control (sw controlled)

LCD_DAT13

+3,3V

-

39

EPDC_BDR01

Panel border control (sw controlled)

LCD_DAT18

+3,3V

-

40

EPDC_SDCE00

Source driver chip enable/start-pulse

LCD_VSYNC

+3,3V

-

3

EPDC_SDCE01

Source driver chip enable/start-pulse

LCD_DAT21

+3,3V

-

47

EPDC_SDCE02

Source driver chip enable/start-pulse

LCD_DAT22

+3,3V

-

51

EPDC_SDCE03

Source driver chip enable/start-pulse

LCD_DAT23

+3,3V

-

26

EPDC_SDDO00

source Driver Data

LCD_DAT00

+3,3V

-

24

EPDC_SDDO01

source Driver Data

LCD_DAT01

+3,3V

-

16

EPDC_SDDO02

source Driver Data

LCD_DAT02

+3,3V

-

18

EPDC_SDDO03

source Driver Data

LCD_DAT03

+3,3V

-

22

EPDC_SDDO04

source Driver Data

LCD_DAT04

+3,3V

-

30

EPDC_SDDO05

source Driver Data

LCD_DAT05

+3,3V

-

28

EPDC_SDDO06

source Driver Data

LCD_DAT06

+3,3V

-

36

EPDC_SDDO07

source Driver Data

LCD_DAT07

+3,3V

-

55

EPDC_SDDO08

source Driver Data

ENET2_RX_DATA0

+3,3V

-

37

EPDC_SDDO09

source Driver Data

ENET2_RX_DATA1

+3,3V

-

35

EPDC_SDDO10

source Driver Data

ENET2_RX_EN

+3,3V

-

43

EPDC_SDDO11

source Driver Data

ENET2_TX_DATA0

+3,3V

-

57

EPDC_SDDO12

source Driver Data

ENET2_TX_DATA1

+3,3V

-

45

EPDC_SDDO13

source Driver Data

ENET2_TX_EN

+3,3V

-

53

EPDC_SDDO14

source Driver Data

ENET2_TX_CLK

+3,3V

-

41

EPDC_SDDO15

source Driver Data

ENET2_RX_ER

+3,3V

Table 17

D N :

3 7