20

DS1113F1

CS4399

3 Characteristics and Specifications

Rise time of SCL and SDA

Standard Mode

Fast Mode

Fast Mode Plus

t

RC

—

—

—

1000

300

120

ns

ns

ns

Fall time of SCL and SDA

Standard Mode

Fast Mode

Fast Mode Plus

t

FC

—

—

—

300

300

120

ns

ns

ns

Setup time for stop condition

t

SUSP

260

—

ns

SDA setup time to SCL rising

t

SUD

50

—

ns

SDA input hold time from SCL falling

4

t

HDDI

0

—

ns

Output data valid (Data/Ack)

5

Standard Mode

Fast Mode

Fast Mode Plus

t

VDDO

—

—

—

3450

900

450

ns

ns

ns

Bus free time between transmissions

t

BUF

500

—

ns

SDA bus capacitance

SCL frequency = 1 MHz, V

L

= 1.8 V

SCL frequency

≤

400 kHz

C

B

—

—

400

400

pF

pF

SCL/SDA pull-up resistance

V

L

= 1.8 V

R

P

350

—

Ω

Pulse width of spikes to be suppressed

t

PS

—

50

ns

Switching time between RCO and MCLK_INT

6

—

150

—

µs

Power-up delay (delay before I

2

C can communicate after RESET released)

t

PUD

1500

—

µs

1.The minimum R

P

value (resistor shown in

) is determined by using the maximum level of VL, the minimum sink current strength of its

respective output, and the maximum low-level output voltage V

OL

. The maximum R

P

value may be determined by how fast its associated signal must

transition (e.g., the lower the value of R

P

, the faster the I

2

C bus is able to operate for a given bus load capacitance). See I²C bus specification

referenced in

.

2.All timing is relative to thresholds specified in

, V

IL

and V

IH

for input signals, and V

OL

and V

OH

for output signals.

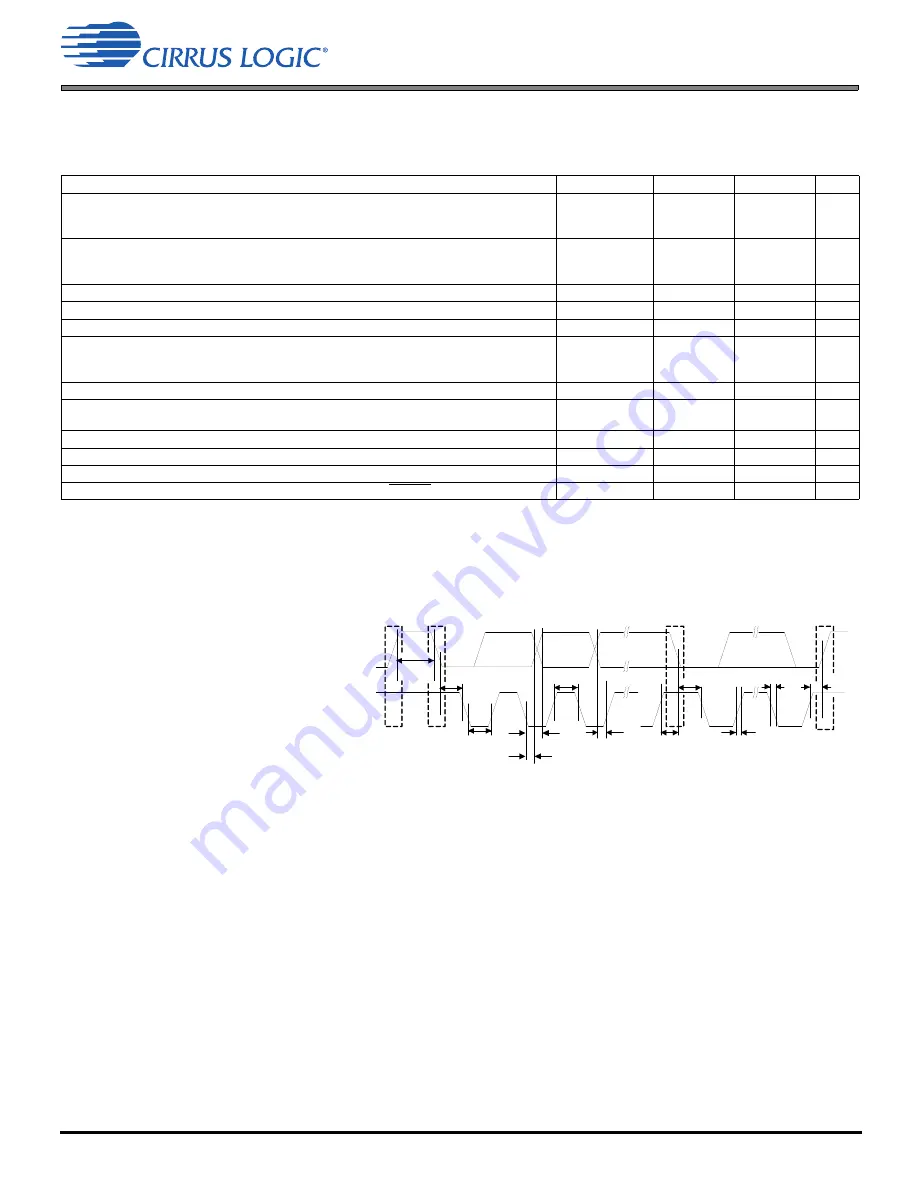

3.I²C control-port timing

4.Data must be held long enough to bridge the transition time, t

F

, of SCL.

5.Time from falling edge of SCL until data output is valid.

6.Upon setting MCLK_SRC_SEL and sending the I

2

C stop condition, the switching of RCO and other MCLK_INT sources occurs. A least wait

time as specified is required after changing MCLK_SRC_SEL and sending the I

2

C stop condition before the next I

2

C transaction is initiated.

Table 3-17. I

2

C Slave Port Characteristics

(Cont.)

Test conditions (unless specified otherwise):

Fig. 2-1

shows typical connections; Inputs: GNDA = GNDL = GNDCP = 0 V; all voltages with respect to

ground; VL = 1.8 V; inputs: Logic 0 = GNDA = 0 V, Logic 1 = VL; T

A

= +25°C; SDA load capacitance equal to maximum value of C

B

= 400 pF; minimum

SDA pull-up resistance, R

P(min)

.

1

Table 3-1

describes some parameters in detail. All specifications are valid for the signals at the pins of the CS4399 with

the specified load capacitance.

Parameter

2

Symbol

3

Minimum

Maximum

Units

t

BUF

t

LOW

Stop

t

HDDI

t

SUD

t

SUST

t

RC

t

HDST

t

HIGH

t

HDST

t

FC

t

SUSP

Start

Repeated

Start

Stop

SDA

SCL

t

VDDO