ADE9000 Technical Reference Manual

UG-1098

Rev. 0 | Page 61 of 86

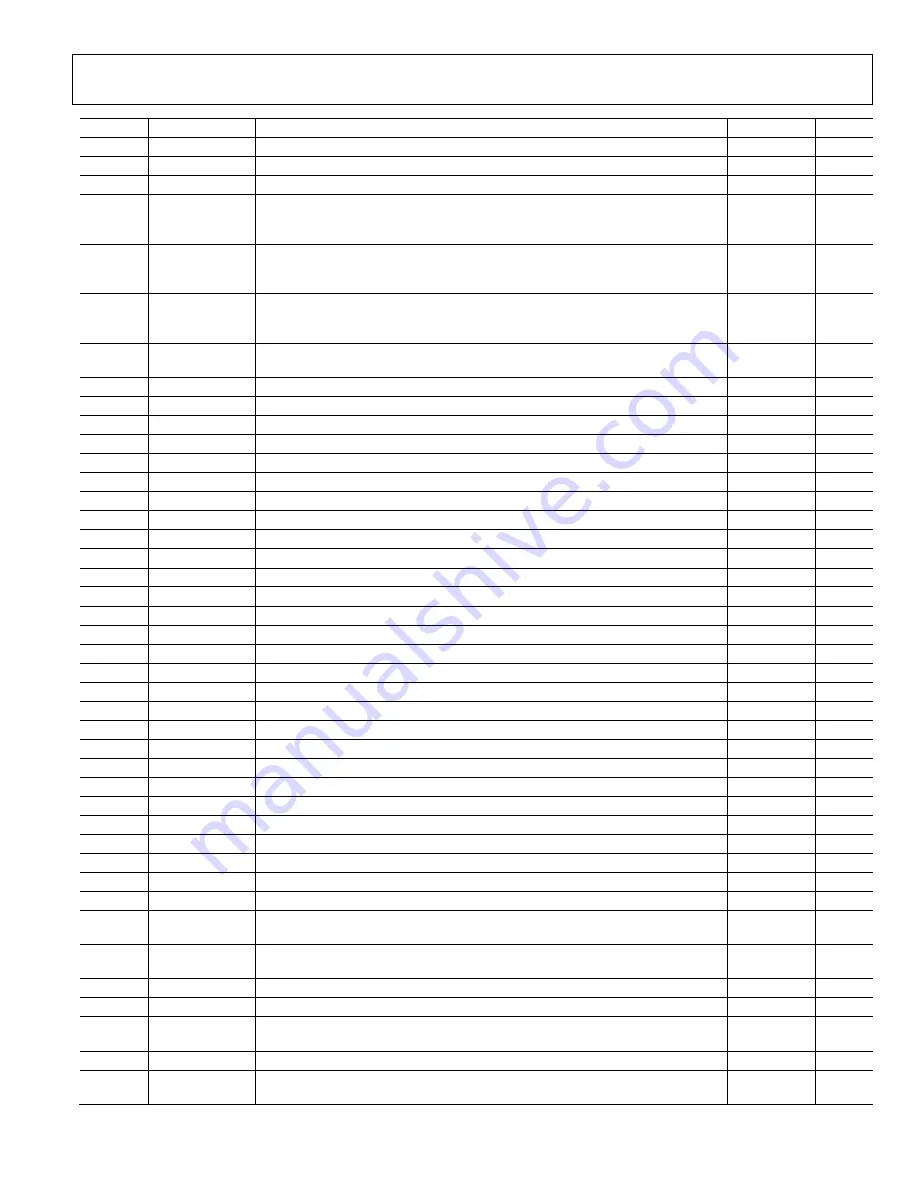

Address

Name

Description

Reset

Access

0x41D

REACT_NL_LVL

No load threshold in the total and fundamental reactive power datapath.

0x0000FFFF

R/W

0x41E

APP_NL_LVL

No load threshold in the total and fundamental apparent power datapath.

0x0000FFFF

R/W

0x41F

PHNOLOAD

Phase no load register.

0x00000000

R

0x420

WTHR

Sets the maximum output rate from the digital to frequency converter for the

total and fundamental active power for the CFx calibration pulse output. It is

recommended to write WTHR = 0x0010_0000.

0x0000FFFF

R/W

0x421

VARTHR

Sets the maximum output rate from the digital to frequency converter for the

total and fundamental reactive power for the CFx calibration pulse output. It is

recommended to write VARTHR = 0x0010_0000.

0x0000FFFF

R/W

0x422

VATHR

Sets the maximum output rate from the digital to frequency converter for the

total and fundamental apparent power for the CFx calibration pulse output. It is

recommended to write VATHR = 0x0010_0000.

0x0000FFFF

R/W

0x423

LAST_DATA_32

This register holds the data read or written during the last 32-bit transaction on

the SPI port.

0x00000000

R

0x424

ADC_REDIRECT

This register allows any ADC output to be redirected to any digital datapath.

0x001FFFFF

R/W

0x425

CF_LCFG

CFx calibration pulse width configuration register.

0x00000000

R/W

0x472

PART_ID

This register identifies the IC. If the ADE9000_ID bit = 1, the IC is the

0x00100000

R

0x474

TEMP_TRIM

Temperature sensor gain and offset, calculated during the manufacturing process.

0x00000000

R/W

0x480

RUN

Write this register to 1 to start the measurements.

0x0000

R/W

0x481

CONFIG1

Configuration Register 1.

0x0000

R/W

0x482

ANGL_VA_VB

Time between positive to negative zero-crossings on Phase A and Phase B voltages.

0x0000

R

0x483

ANGL_VB_VC

Time between positive to negative zero-crossings on Phase B and Phase C voltages.

0x0000

R

0x484

ANGL_VA_VC

Time between positive to negative zero-crossings on Phase A and Phase C voltages.

0x0000

R

0x485

ANGL_VA_IA

Time between positive to negative zero-crossings on Phase A voltage and current.

0x0000

R

0x486

ANGL_VB_IB

Time between positive to negative zero-crossings on Phase B voltage and current.

0x0000

R

0x487

ANGL_VC_IC

Time between positive to negative zero-crossings on Phase C voltage and current.

0x0000

R

0x488

ANGL_IA_IB

Time between positive to negative zero-crossings on Phase A and Phase B current.

0x0000

R

0x489

ANGL_IB_IC

Time between positive to negative zero-crossings on Phase B and Phase C current.

0x0000

R

0x48A

ANGL_IA_IC

Time between positive to negative zero-crossings on Phase A and Phase C current.

0x0000

R

0x48B

DIP_CYC

Voltage RMS½ dip detection cycle configuration.

0xFFFF

R/W

0x48C

SWELL_CYC

Voltage RMS½ swell detection cycle configuration.

0xFFFF

R/W

0x48F

OISTATUS

Overcurrent status register.

0x0000

R

0x490

CFMODE

CFx configuration register.

0x0000

R/W

0x491

COMPMODE

Computation mode register.

0x0000

R/W

0x492

ACCMODE

Accumulation mode register.

0x0000

R/W

0x493

CONFIG3

Configuration Register 3.

0xF000

R/W

0x494

CF1DEN

CF1 denominator register.

0xFFFF

R/W

0x495

CF2DEN

CF2 denominator register.

0xFFFF

R/W

0x496

CF3DEN

CF3 denominator register.

0xFFFF

R/W

0x497

CF4DEN

CF4 denominator register.

0xFFFF

R/W

0x498

ZXTOUT

Zero-crossing timeout configuration register.

0xFFFF

R/W

0x499

ZXTHRSH

Voltage channel zero-crossing threshold register.

0x0009

R/W

0x49A

ZX_LP_SEL

This register selects which zero-crossing and which line period measurement are

used for other calculations.

0x001E

R/W

0x49C

SEQ_CYC

Number of line cycles used for phase sequence detection. It is recommended to

set this register to 1.

0x00FF

R/W

0x49D

PHSIGN

Power sign register.

0x0000

R

0x4A0

WFB_CFG

Waveform buffer configuration register.

0x0000

R/W

0x4A1

WFB_PG_IRQEN This register enables interrupts to occur after specific pages of the waveform

buffer are filled.

0x0000

R/W

0x4A2

WFB_TRG_CFG

This register enables events to trigger a capture in the waveform buffer.

0x0000

R/W

0x4A3

WFB_TRG_STAT

This register indicates the last page that was filled in the waveform buffer and

the location of trigger events.

0x0000

R/W