– 53 –

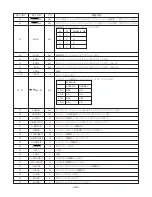

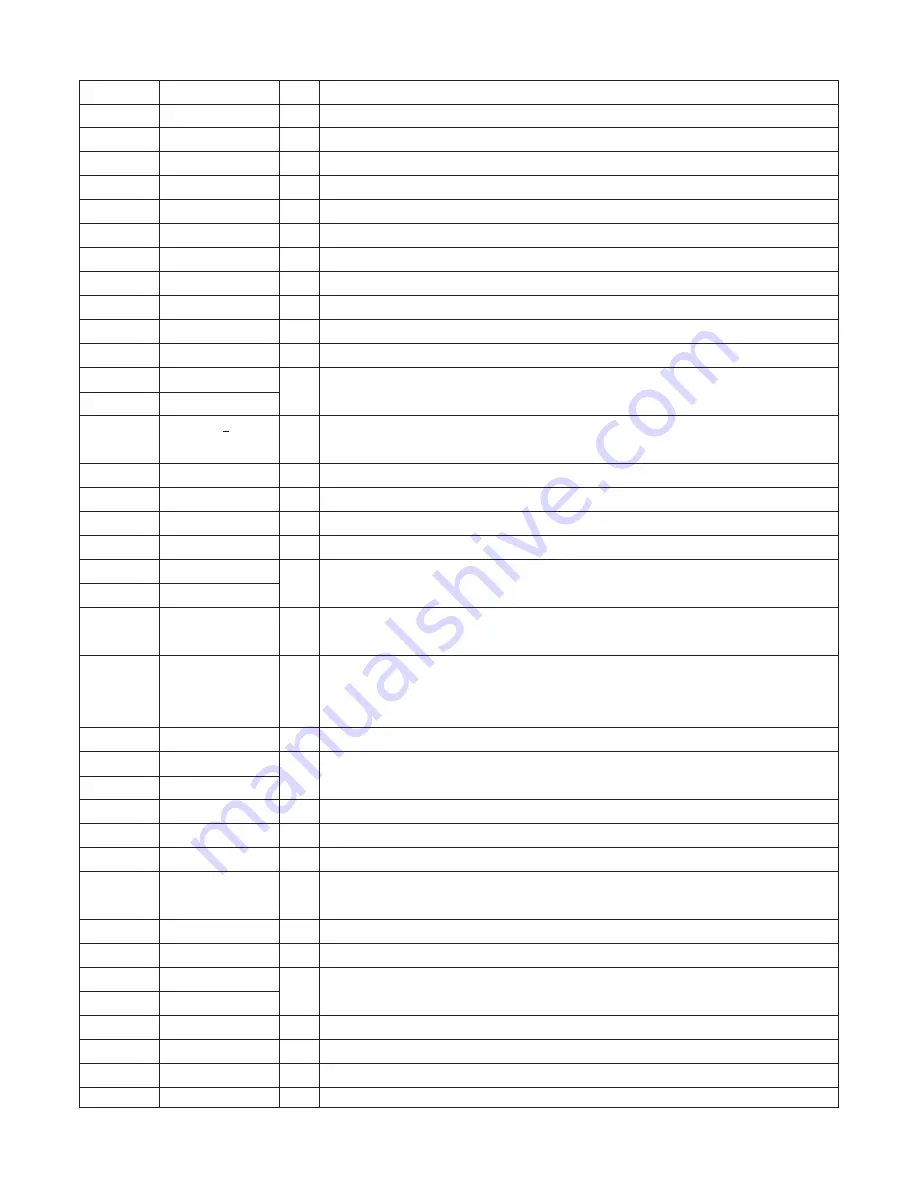

1

DEFI

I

Defect detection signal (DEF) input.

2

TAI

I

Test input. A pull-down resistor is built in. Must be connected to 0V.

3

PDO

O

External VCO control phase comparator output.

4

VVSS

–

Internal VCO ground. Must be connected to 0V.

5

ISET

I

PDO output current adjustment resistor connection.

6

VVDD

–

Internal VCO power supply.

7

FR

I

VCO frequency range adjustment.

8

VSS

–

Digital system ground. Must be connected to 0V.

9

EFMO

O

Slice level control; EFM signal output.

10

EFMIN

I

Slice level control; EFM signal input.

11

T2

I

Test input. A pull-down resistor is built in. Must be connected to 0V.

12

CLV+

O

Disc motor control output.

13

CLV–

Three-value ouput is also possible when specified by microprocessor command.

14

V/P

O

Rough servo/phase control automatic switching monitor output. Outputs a high level

during rough servo and a low level during phase control.

15

HFL

I

Track detection signal input. This is a Schmitt input.

16

TES

I

Tracking error signal input. This is a Schmitt input.

17

TOFF

O

Tracking off output.

18

TGL

O

Tracking gain switching output. Increase the gain when low.

19

JP+

O

Track jump output.

20

JP–

Three-value output is also possible when specified by microprocessor command.

21

PCK

O

EFM data playback clock monitor. Outputs 4.3218 MHz when the phase is locked.

(Not used)

Synchronization signal detection ouput. Outputs a high level when the synchronization

22

FSEQ

O

signal detected from the EFM signal and the internally generated synchronization signal

agree. (Not used)

23

VDD

–

Digital system power supply.

24

SL+

O

Serial data command sled signal output terminal from microprocessor.

25

SL–

26

NC

–

Not used.

27

PU IN

I

CD pickup inside limit switch.

28

CD R/W

O

Serial data command sled signal output terminal from microprocessor.

29

EMPH

O

De-emphasis monitor pin. A high level indicates playback of a de-emphasis disk.

(Not used)

30

C2F

O

C2 flag output. (Not used)

31

DOUT

O

Digital output (EIAJ format).

32

T3

I

Test input. A pull-down resistor is built in. Must be connected to 0V.

33

T4

34

NC

–

Unused. Must be left open.

35

MUTEL

O

Left channel one-bit D/A converter mute output. (Not used)

36

LVDD

–

Left channel one-bit D/A converter power supply.

37

LCHO

O

Left channel one-bit D/A converter output.

Pin No.

Pin Name

I/O

Description

IC, LC78622ED

Summary of Contents for XR-MD510

Page 5: ... 5 ...

Page 15: ... 15 SCHEMATIC DIAGRAM 1 MAIN PT1 PT2 RELAY ...

Page 17: ... 17 SCHEMATIC DIAGRAM 2 FRONT SW 1 SW 2 FACE A FACE B FACE C DECK ...

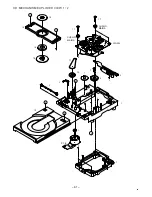

Page 20: ... 20 SCHEMATIC DIAGRAM 3 CD CD LOAD CD DRIVE ...

Page 22: ... 22 SCHEMATIC DIAGRAM 4 D TUNER ...

Page 24: ... 24 SCHEMATIC DIAGRAM 5 K TUNER ...

Page 26: ... 26 SCHEMATIC DIAGRAM 6 EZ TUNER ...

Page 29: ... 29 IC BLOCK DIAGRAM IC BA5936S IC BU2099FV ...

Page 30: ... 30 IC BU2092F IC BU1920FS ...

Page 31: ... 31 IC MM1454XFBE IC LA1837NL ...

Page 32: ... 32 IC TA2040AF IC HA12211 ...

Page 33: ... 33 IC CXA1553P IC LC72131D ...

Page 34: ... 34 IC BD3876KS2 ...

Page 38: ... 38 8 SFR130 TP3 VREF TP2 FE C CD C B L201 7 TP1 K SCAN GND IC201 7 B FRONT C B ...

Page 43: ... 43 98 O ARDY O 99 O SREQ O 100 I MREQ I ja ja 01234 ja 0123 fLl ...

Page 55: ... 55 FL 13 ST 44GNK ACJ 4 GRID ASSIGNMENT ANODE CONNECTION GRID ASSIGNMENT ...

Page 56: ... 56 ANODE CONNECTION ...