SERIES I/O SERVER MODULE

MIL-STD-1553A/B Bus Interface Module

________________________________________________________________________

14

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:[email protected]

www.acromag.com

Address decoding of eighteen of the IOS address signals A (1:18) is implemented in the

FPGA, in conjunction with the IOS select signals, to identify access to the IOS modules

MEM, INT, ID or I/O spaces. In addition, the byte strobes BS0 and BS1 are decoded to

identify low byte, high byte, or double byte data transfers.

The carrier to IOS module interface implements access to MEM, INT, ID and I/O space via

16 or 8-bit data transfers. Read only access to ID space provides the identification for the

module (as given in Table 1). Read and write access to the I/O space provides a means to

control the IOS-57x and monitor status. Reads and writes to MEM space provide access to

the Micro ACE 1553 controllers.

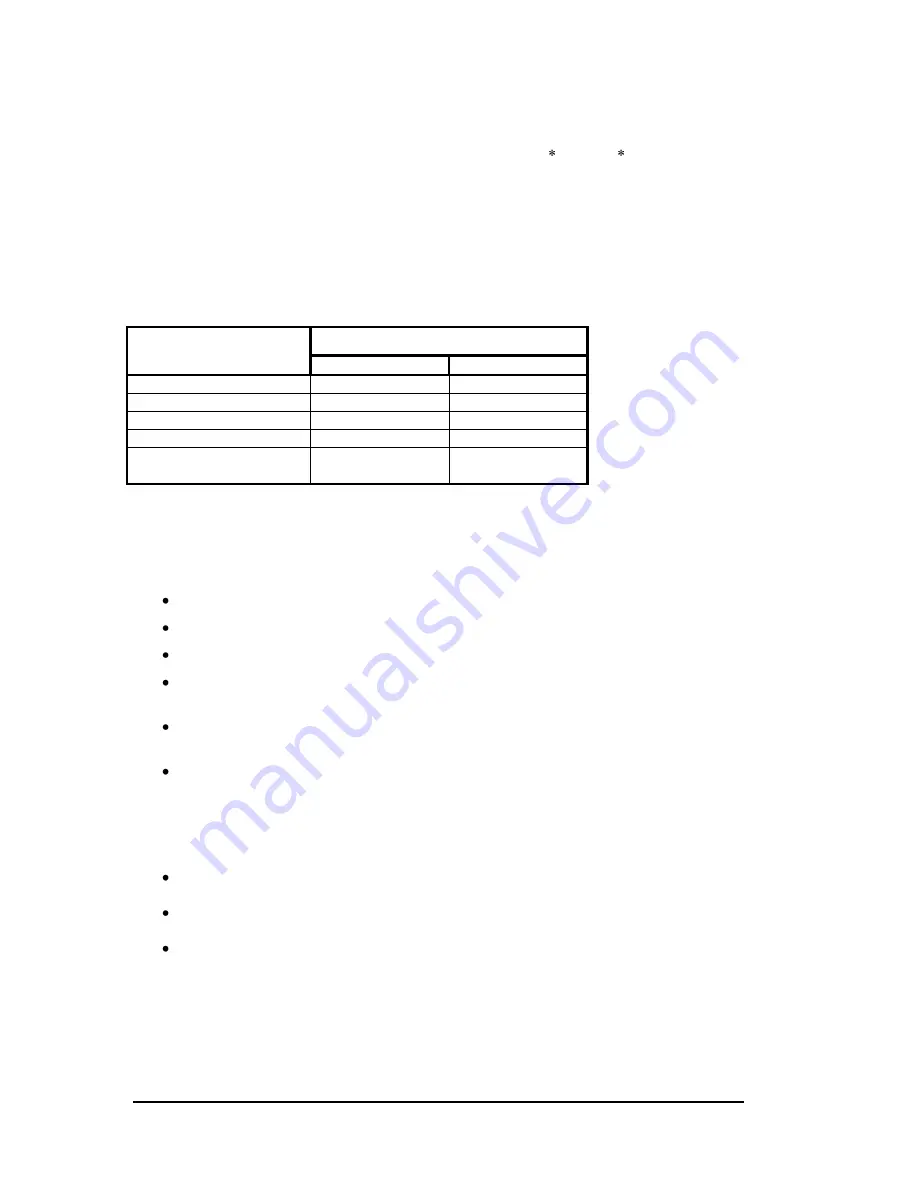

The timing for access to the various address spaces is shown in Table 9.

Table 9 Access Times

Address Space

Wait States

Read

Write

INT

1

0

ID

1

N/A

I/O

1

0

MEM (8 MHz IOS clock)

3

3

MEM (32 MHz IOS

clock)

8

8

IOS-57xCONTROL LOGIC

All logic to provide access to the Micro ACE 1553 controllers is imbedded in th

e module’s

FPGA. Once the IOS-57x FPGA has been configured, the control logic provides the

following functions:

Source of the 16 MHz clock to the Micro ACE.

Issues interrupt requests to the carrier.

Controls the Micro ACE master clear (reset) signal

Source of the 100 KHz tag clock output signal used to synchronize the IOS-57x

with external devices

Accepts an external TTL level tag clock input signal to synchronize the IOS-57x

with external devices

Provides mode control (inhibit) to each of the Micro ACE dual redundant

transceivers.

TAG CLOCK Input / Output

The TAG clock for each 1553 channel can be selected from three possible sources:

Micro ACE internal time tag clock, selectable 2µs, 4µs, 8µs, 16µs, 32µs, 64µs

resolution.

FPGA generated 100 KHz clock, provides 10 µs resolution. This clock is also an

output on the P2 connector.

External (P2 connector) tag clock input.

To select the Micro ACE internal time tag clock: write bits TTR2:0 in configuration register

#2 for each 1553 channel with the appropriate pattern for the resolution desired.

To select the FPGA generated 100 KHz clock as the Micro ACE time tag clock: write bits

TTR2:0 in configuration register #2 with the bit pattern “111”. Write the tag clock source

(bit 7) of the IOS I/O space control register with the value 0.