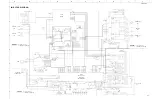

Pin

No.

Port Name

Function Name

(P.C.B.)

I/O

Detail of Function

P

o

w

erOn

Standb

y

MCUSleep

EEP W

riting

[When wr

iting]

66 P2_6/AN2_6/A6

PWR_RY

O

O

O

Power relay control

67 P2_5/INT7/AN2_5/A5

ACPWR_DET

IRQ

O

O

AC power input detection

68 P2_4/INT6/AN2_4/A4

CD_PWR_DET

I

O

O

Vaddis886 SDRAM CLOCK enable control monitor

69 P2_3/AN2_3/A3

SW_CD_OTHER

O

O

O

For switching control between CD and other functions

CD=H, Other=L

70 P2_2/AN2_2/A2

FPGA_JTAGEN

O

O

O

FPGA

L=TDI, TDO, TMS, TCK functions as general purpose I/O

H=TDI, TDO, TMS, TCK functions as JTAG pin

71 P2_1/AN2_1/A1

CD_RST

O

O

O

SA-CD MODULE control reset output

72 P2_0/AN2_0/A0

FPGA_IO2

O

O

O

Communication between CPLDs serial data

73 P1_7/nINT5/IDU/D15

DIR_N_INT

IRQ

O

O

DIR DIX9210 control interrupt input

74 P1_6/nINT4/IDW/D14

CD_MUTE

I

O

O

SA-CD MODULE MUTE detection

75 P1_5/INT3/IDV/D13

CD_SPDIF_RQ

O

O

O

SA-CD MODULE (Vaddis886) control SPDIF request output

76 P1_4/D12

CD_PWR

O

O

O

SA-CD MODULE control power On/Off control

High: On, Low: Off

77 P1_3/TXD6/SDA6/D11

CD_YOVI

SO

O

O

Vaddis886 control data out

78 P1_2/RXD6/SCL6/D10

CD_YIVO

SI

O

O

Vaddis886 control data in

79 P1_1/CLK6/D9

FPGA_IO1

I

O

O

Communication between CPLDs serial clock

80 P1_0/nCTS6/nRTS6/D8

FPGA_IO0

O

O

O

CPLD serial enable

81 P0_7/AN0_7/D7

PRVR

AD

O

O

Analog Rch power voltage protection

82 P0_6/AN0_6/D6

PRVL

AD

O

O

Analog Lch power voltage protection

83 P0_5/AN0_5/D5

PRVD

AD

O

O

Digital power voltage protection

84 P0_4/AN0_4/D4

KEY2

AD

O

O

Key taking AD

85 P0_3/AN0_3/D3

KEY1

AD

O

O

Key taking AD

86 P0_2/AN0_2/D2

KEY0

AD

O

O

Key taking AD

87 P0_1/AN0_1/D1

LOAD-

AD

O

O

LOADER open detection

Using LOADER control signal of Pioneer module, tray open

enable function after CD stop is detected

88 P0_0/AN0_0/D0

LOAD+

AD

O

O

LOADER open detection

Using LOADER control signal of Pioneer module, tray open

enable function after CD stop is detected

89 P10_7/AN7/nKI3

FPGA_DSDMUTE

O

O

O

FPGA DSD MUTE designation / Low=MUTE, High=MUTE Off

90 P10_6/AN6/nKI2

FGA_DOP_DSDPCM

I

O

O

FPGA

Judgment result on DOP's DSD/PCM input / L=PCM, H=DSD

91 P10_5/AN5/nKI1

FPGA_DOP_DSDRATE

I

O

O

FPGA

Judgment result on DOP's DSD normal speed/double speed

input

L=Normal speed, H=Double speed

92 P10_4/AN4/nKI0

EX_N_CS

O

O

O

Extended IC: Chip select for LC709004A

93 P10_3/AN3

EX_N_IC

O

O

O

Extended IC: Initial clear for LC709004A

94 P10_2/AN2

FL_PON

O

O

O

VFL power on control / High=FL power On, Low=FL power Off

95 P10_1/AN1

FL_N__RST

O

O

O

FL driver control reset

96 Avss

MG

MCU

MCU

MCU

D_GND

97 P10_0/AN0

FL_N_CS

O

O

O

FL driver control chip selection

98 Vref

VREF

MCU

MCU

MCU

+5M

99 Avcc

AVCC

MCU

MCU

MCU

+5M

100 P9_7/nADTRG/SIN4

NC

O

O

O

LED_OPT control / High=On, Low=Off

46

CD-S3000

CD-S30

0

0

Содержание CD-S3000

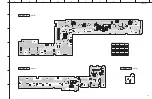

Страница 6: ... FRONT PANELS U K A B G L V J models T model 6 CD S3000 CD S3000 ...

Страница 7: ... REAR PANELS U V models U model V model Bottom view 7 CD S3000 CD S3000 ...

Страница 8: ...A B G L models K model T model A model B G models 8 CD S3000 CD S3000 ...

Страница 9: ...J model 9 CD S3000 CD S3000 ...

Страница 86: ...86 CD S3000 CD S3000 ...

Страница 87: ...MEMO 87 CD S3000 CD S3000 87 ...

Страница 88: ...CD S3000 ...