52

Virtex-6 FPGA Connectivity Kit Getting Started

UG664 (v1.4) July 6, 2011

Modifying the Virtex-6 FPGA Targeted Reference Design

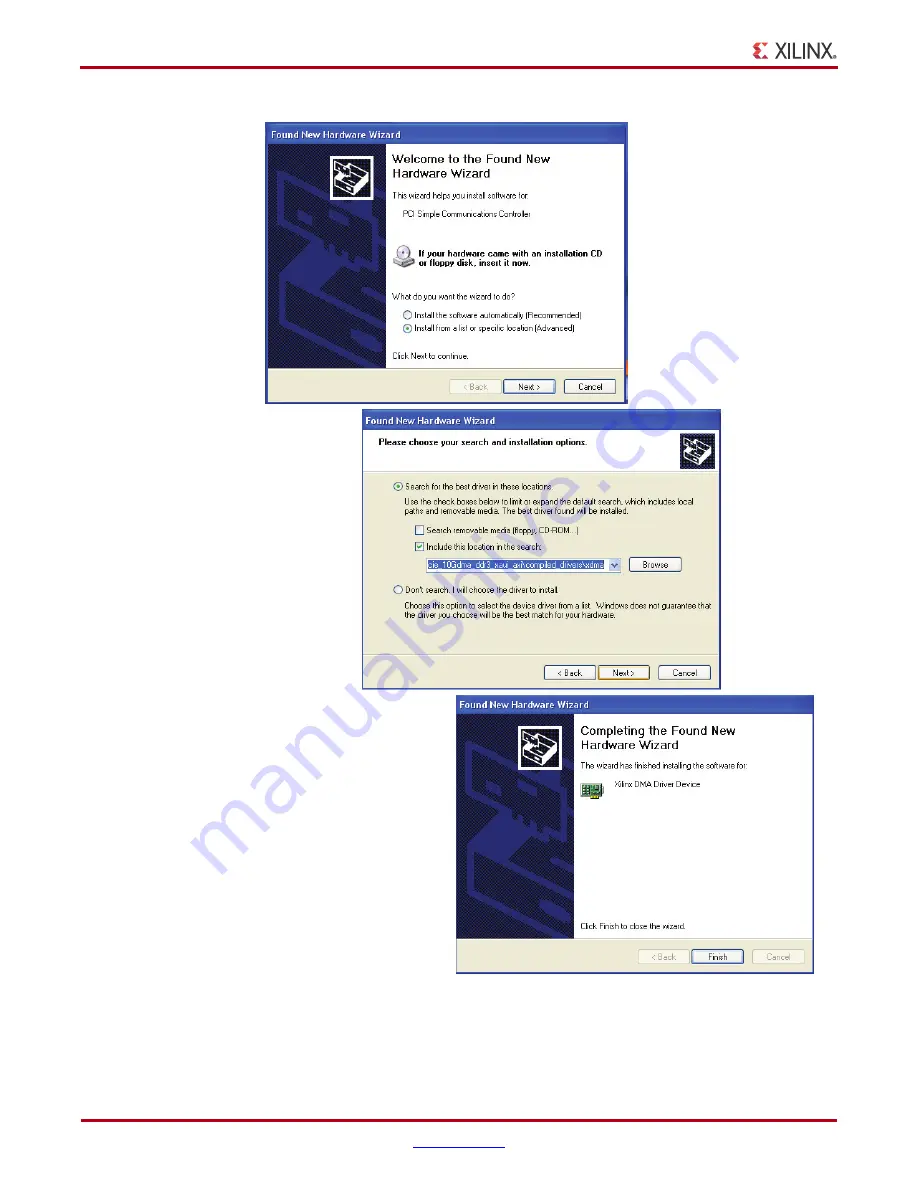

To load the recompiled xrawdata driver, select

Install from a list or specific location

,

and click

Next

. Browse and choose

X-Ref Target - Figure 47

Figure 47:

Load Xilinx DMA Driver

UG664_77_052011

Содержание Virtex-6 FPGA

Страница 1: ...Virtex 6 FPGA Connectivity Kit Getting Started Guide UG664 v1 4 July 6 2011 XPN 0402826 03...

Страница 4: ...Virtex 6 FPGA Connectivity Kit Getting Started www xilinx com UG664 v1 4 July 6 2011...

Страница 6: ...6 www xilinx com Virtex 6 FPGA Connectivity Kit Getting Started UG664 v1 4 July 6 2011...