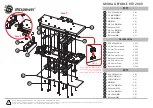

• 2 x 25G external SFP connectors in Zynq Ult MPSoC

• ZU21 Zynq Ult RFSoC PCIe x8 interface

• ZU19 Zynq Ult MPSoC PCIe x8 interface

• ZU19 Zynq Ult MPSoC

• ZU21 Zynq Ult RFSoC PS/PL DDR4

100G Internal Connection between

Zynq Ult MPSoC and

Zynq Ult RFSoC

The 100G interface is made into 4 x 25G lanes at four ports. Data can be pumped from the PCIe

of the Zynq Ult MPSoC and Zynq Ult RFSoC using the DPDK pktgen

application. The Xilinx QDMA IP core is used for sending or receiving data to or from the host.

All 4 x 25G lanes are mapped to queues 1,2,3, and 4 of the QDMA core respectively in the

Zynq Ult MPSoC and Zynq Ult RFSoC devices. Data transferred from the

Zynq Ult MPSoC reaches the Zynq Ult RFSoC through this internal interface,

and vice versa.

Test Procedure

1. Set up the system as shown in the following figure.

DPDK-Pktgen Port0

MPSoC

25G_0

25G_1

25G_2

25G_3

Host

25G_0

25G_1

25G_2

25G_3

PCIe

X8

RFSoC

25G_0

25G_1

25G_2

25G_3

PCIe

X8

DPDK-Pktgen Port1

T1 Telco Accelerator Card

Host

Queue 1_25G_lane0

Queue 2_25G_lane1

Queue 3_25G_lane2

Queue 4_25G_lane3

X25236-033121

2. Ensure the conditions in the

Chapter 2: Card Information and Installation

met.

3. Run the

test.sh

in root, with

init

as argument, to initialize the DMA and DPDK drivers.

Chapter 6: Running the Tests

UG1518 (v1.0) December 17, 2021

T1 Telco Accelerator Card Installation Guide

21