6. Packaging

213

Tsi308 User Manual

80D4000_MA001_02

Tundra Semiconductor Corporation

www.tundra.com

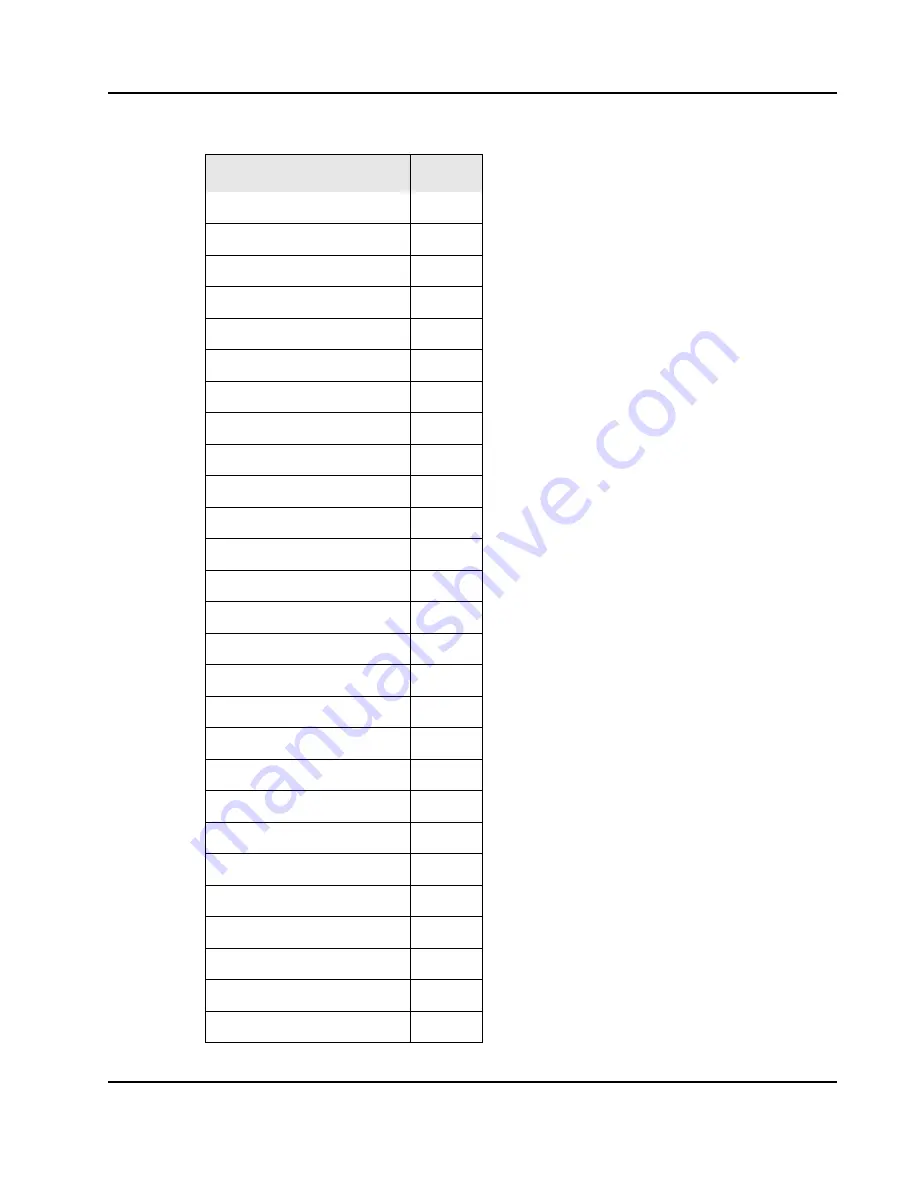

L1_TX_CAD_H[0]

F25

L1_TX_CAD_H[1]

G24

L1_TX_CAD_H[2]

F26

L1_TX_CAD_H[3]

J25

L1_TX_CAD_H[4]

K25

L1_TX_CAD_H[5]

K26

L1_TX_CAD_H[6]

L25

L1_TX_CAD_H[7]

M26

L1_TX_CAD_L[0]

G25

L1_TX_CAD_L[1]

H24

L1_TX_CAD_L[2]

G26

L1_TX_CAD_L[3]

J24

L1_TX_CAD_L[4]

K24

L1_TX_CAD_L[5]

L26

L1_TX_CAD_L[6]

L24

L1_TX_CAD_L[7]

N26

L1_TX_CLK_H

H26

L1_TX_CLK_L

J26

L1_TX_CTL_H

N25

L1_TX_CTL_L

N24

LDTSTOP_N

AE3

NONFATAL_ERR_N

AF2

P0_ACK64_N

C19

P0_AD0

D5

P0_AD1

C5

P0_AD10

C8

P0_AD11

A8

Table 35: Tsi308 Sorted by Name

Pin Name

Pin #

Содержание TSI308

Страница 4: ...4 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...

Страница 6: ...6 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...

Страница 12: ...Contents 12 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...

Страница 14: ...List of Figures 14 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...

Страница 20: ...20 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...

Страница 69: ...2 Interface Operation 69 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...

Страница 70: ...2 Interface Operation 70 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...

Страница 187: ...4 Register Descriptions 187 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...

Страница 188: ...4 Register Descriptions 188 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...

Страница 258: ...9 Ordering Information 258 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...

Страница 260: ...Index 260 Tsi308 User Manual 80D4000_MA001_02 Tundra Semiconductor Corporation www tundra com ...