Page 16

2. CPU Core

2.3 System clock controller

TMP89FM42

RA001

Note 3: If the STOP mode is activated with SYSCR1<OUTEN> set at "0", the port internal input is fixed to "0". Therefore, an exter-

nal interrupt may be set at the falling edge, depending on the pin state when the STOP mode is activated.

Note 4: The P11 pin is also used as the STOP pin. When the STOP mode is activated, the pin reverts to high impedance state and

is put in input mode, regardless of the state of SYSCR1<OUTEN>.

Note 5: Writing of the second byte data will be executed improperly if the operation is switched to the STOP state by an instruc-

tion, such as LDW, which executes 2-byte data transfer at a time.

Note 6: Don't set SYSCK1<DV9CK> to "1" before the oscillation of the low-frequency clock oscillation circuit becomes stable.

Note 7: In the SLOW1/2 or SLEEP1 mode, fs/4 is input to stage 9 of the divider, regardless of the state of SYSCR1< DV9CK >.

Note 1: fcgck: Gear clock [Hz], fs: Low-frequency clock [Hz]

Note 2: WDT: Watchdog timer, TG: Timing generator

Note 3: Don't set both SYSCR2<IDLE> and SYSCR2<TGHALT> to "1" simultaneously.

Note 4: Writing of the second byte data will be executed improperly if the operation is switched to the IDLE state by an instruction,

such as LDW, which executes 2-byte data transfer at a time.

Note 5: When the IDLE1/2 or SLEEP1 mode is released, SYSCR2<IDLE> is cleared to "0" automatically.

Note 6: When the IDLE0 or SLEEP0 mode is released, SYSCR2<TGHALT> is cleared to "0" automatically.

Note 7: Bits 7, 1 and 0 of SYSCR2 are read as "0".

Note 1: fc: High-frequency clock [Hz], fs: Low-frequency clock [Hz]

Note 2: WUCCR<WUCRST> is cleared to "0" automatically, and need not be cleared to "0" after being set to "1".

Note 3: Bits 7 to 4 of WUCCR are read as "0". Bit 0 is read as "1".

Note 4: Before starting the warm-up counter operation, set the source clock and the frequency division rate at WUCCR and set

the warm-up time at WUCDR.

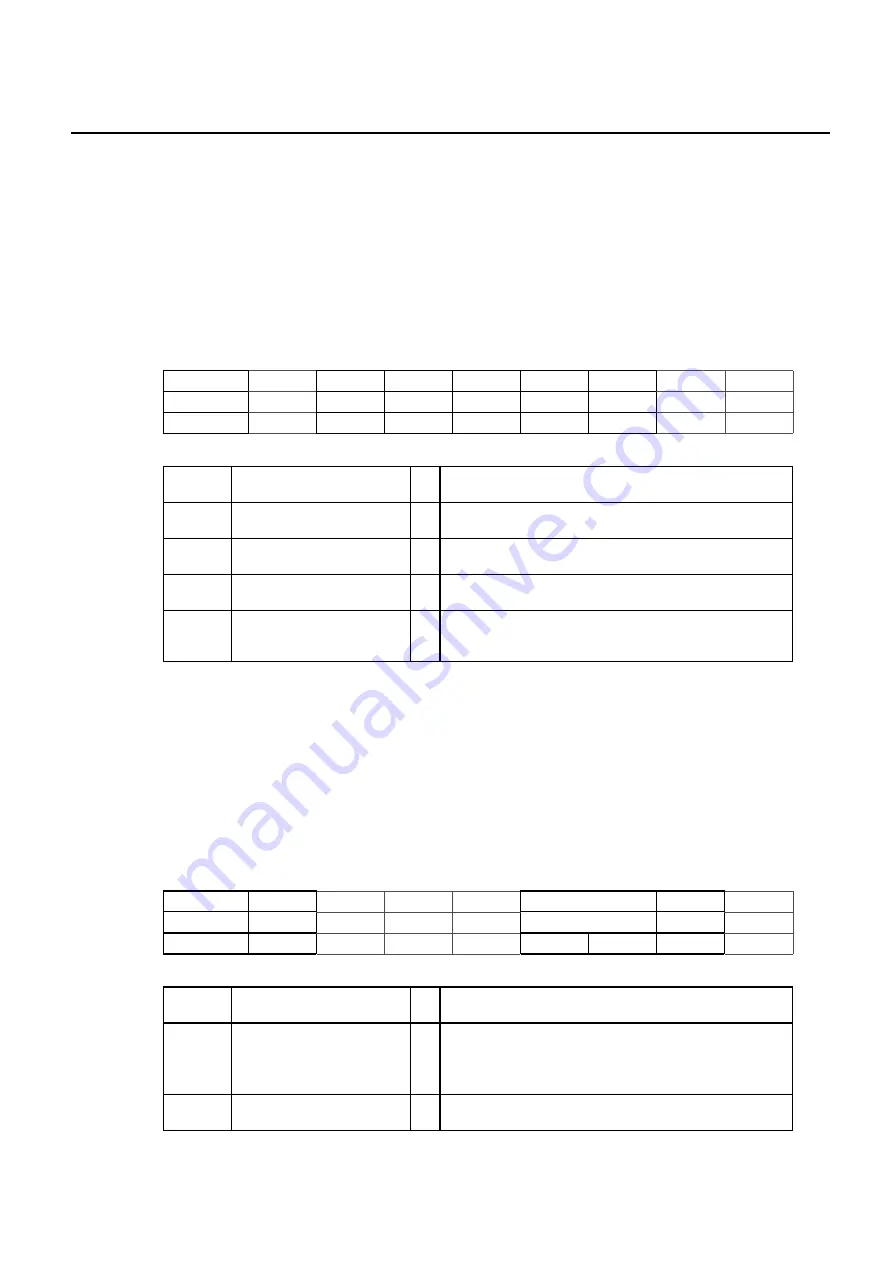

System control register 2

SYSCR2

(0x0FDD)

7

6

5

4

3

2

1

0

Bit Symbol

-

XEN

XTEN

SYSCK

IDLE

TGHALT

-

-

Read/Write

R

R/W

R/W

R/W

R/W

R/W

R

R

After reset

0

1

0

0

0

0

0

0

XEN

Controls the high-frequency clock

oscillation circuit

0 :

1 :

Stop oscillation

Continue or start oscillation

XTEN

Controls the low-frequency clock

oscillation circuit

0 :

1 :

Stop oscillation

Continue or start oscillation

SYSCK

Selects a system clock

0 :

1 :

Gear clock (fcgck) (NORMAL1/2 or IDLE1/2 mode)

Low-frequency clock (fs/4) (SLOW1/2 or SLEEP1 mode)

IDLE

CPU and WDT control

(IDLE1/2 or SLEEP1 mode)

0 :

1 :

Operate the CPU and the WDT

Stop the CPU and the WDT (Activate IDLE1/2 or SLEEP1 mode)

TGHALT

TG control

(IDLE0 or SLEEP0 mode)

0 :

1 :

Enable the clock supply from the TG to all the peripheral circuits

Disable the clock supply from the TG to the peripheral circuits except the

TBT (Activate IDLE0 or SLEEP0 mode)

Warm-up counter control register

WUCCR

(0x0FCD)

7

6

5

4

3

2

1

0

Bit Symbol

WUCRST

-

-

-

WUCDIV

WUCSEL

-

Read/Write

W

R

R

R

R/W

R/W

R

After reset

0

0

0

0

1

1

0

1

WUCRST

Resets and stops the warm-up

counter

0 :

1 :

-

Clear and stop the counter

WUCDIV

Selects the frequency division of the

warm-up counter source clock

00 :

01 :

10 :

11 :

Source clock

Source clock / 2

Source clock / 2

2

Source clock / 2

3

WUCSEL

Selects the warm-up counter

source clock

0 :

1 :

Select the high-frequency clock (fc)

Select the low-frequency clock (fs)

Содержание TLCS-870/C1 Series

Страница 1: ...8 Bit Microcontroller TLCS 870 C1 Series TMP89FM42 查询TMP89FM42供应商 捷多邦 专业PCB打样工厂 24小时加急出货 ...

Страница 3: ...Revision History Date Revision 2007 10 25 1 First Release 2007 11 3 2 Contents Revised ...

Страница 4: ......

Страница 14: ......

Страница 18: ...1 3 Block Diagram TMP89FM42 1 3 Block Diagram Figure 1 2 Block Diagram ...

Страница 22: ...1 4 Pin Names and Functions TMP89FM42 ...

Страница 60: ...2 CPU Core 2 5 Revision History TMP89FM42 ...

Страница 76: ...3 Interrupt Control Circuit 3 8 Revision History TMP89FM42 ...

Страница 86: ...4 External Interrupt control circuit 4 3 Function TMP89FM42 ...

Страница 102: ...7 Voltage Detection Circuit 7 5 Revision History TMP89FM42 ...

Страница 126: ...8 I O Ports 8 3 I O Port Registers TMP89FM42 Note 2 i 0 to 1 ...

Страница 136: ...8 I O Ports 8 5 Revision History TMP89FM42 ...

Страница 142: ...9 Special Function Registers 9 3 SFR3 0x0E40 to 0x0EFF TMP89FM42 ...

Страница 146: ...10 Low Power Consumption Function for Peripherals TMP89FM42 ...

Страница 149: ...TMP89FM42 11 3 Revision History Rev Description RA001 Deleted SLEEP2 description ...

Страница 150: ...11 Divider Output DVO 11 3 Revision History TMP89FM42 ...

Страница 220: ...15 Real Time Clock RTC 15 4 Real Time Clock Operation TMP89FM42 ...

Страница 250: ...16 Asynchronous Serial Interface UART 16 15 Revision History TMP89FM42 ...

Страница 302: ...18 Serial Bus Interface SBI 18 7 Revision History TMP89FM42 ...

Страница 336: ...21 Flash Memory 21 4 Toggle Bit D6 TMP89FM42 Note 1 Make sure that you set the C register to 0x00 LD FLSCR2 0xD5 ...

Страница 338: ...21 Flash Memory 21 4 Toggle Bit D6 TMP89FM42 ...

Страница 384: ...22 Serial PROM Mode 22 15 Revision History TMP89FM42 ...

Страница 388: ...24 Input Output Circuit 24 1 Control Pins TMP89FM42 ...

Страница 404: ...25 Electrical Characteristics 25 11 Revision History TMP89FM42 ...

Страница 406: ...26 Package Dimensions TMP89FM42 ...

Страница 408: ......