Software Control

2.2.4.3

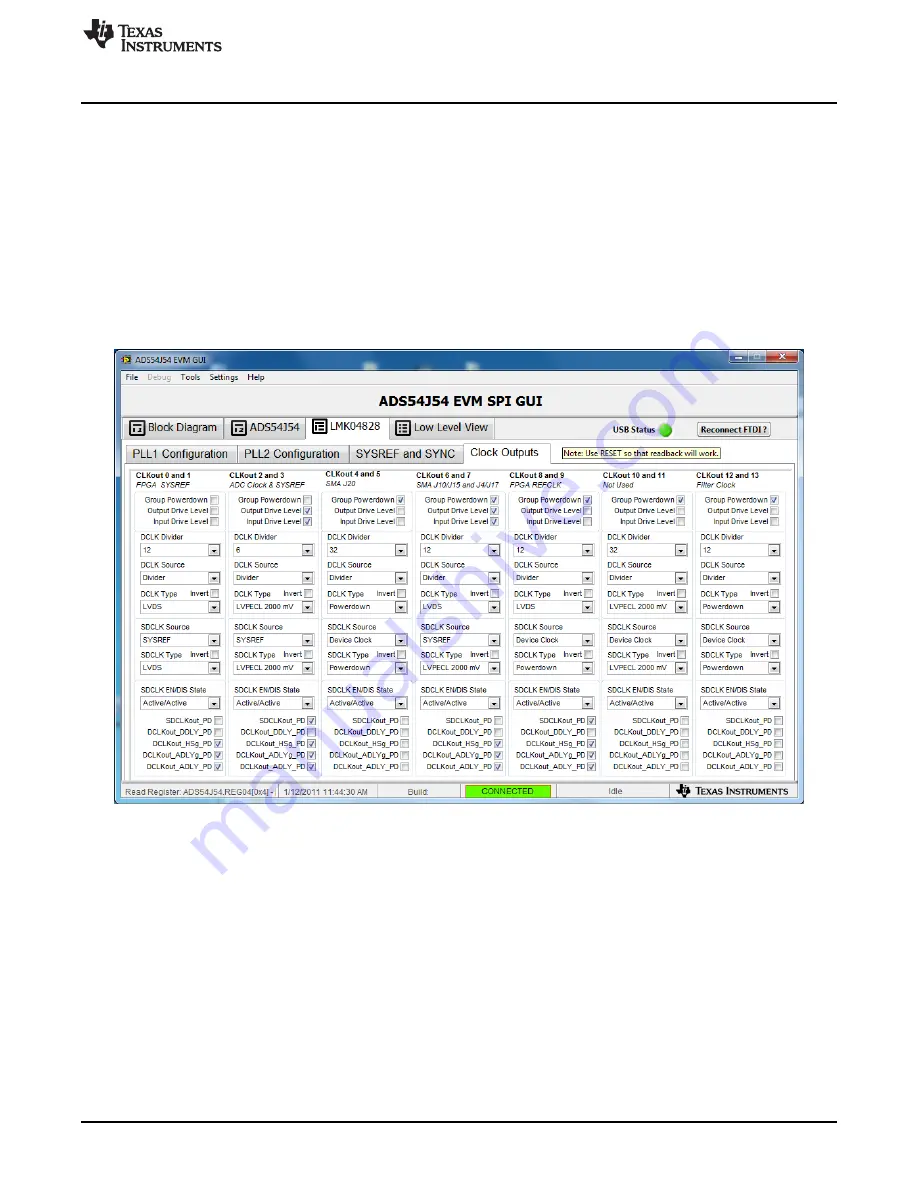

Clock Output Controls

Clicking

Clock Outputs

opens the LMK04828 Clock Outputs tab, shown in

. This tab is organized

into 7 sections representing the 7 pairs of DCLK/SYSREF that the LMK04828 can generate. For each of

the 7 pairs of DCLK/SYSREF, there are a number of controls that apply to both outputs, such as the

option to power down the pair of signals completely, if not needed. For both DCLK and SYSREF, there is

an option to select what type of output driver is to be used, such as LVDS or LVPECL. There are controls

to enable things like delay or inversion. For the DCLK, there is a control to select a divider ration to divide

the PLL2 VCO clock down to the desired output frequency. For example, if the ADS54J54 EVM is to be

operated at 500 Msps, then the configuration file supplied with the GUI will select the 3.0-GHz VCO and

select a divider ratio of 6 to generate a 500-MHz DCLK. If the TSW14J56 capture card is used, the

TSW14J56 needs to see a DCLK reference that is one-twentieth the line rate of the serial data stream so

the divider ratio chosen is 12 to generate a 250-MHz DCLK to the FMC connector. These two divider

ratios can be seen in

Figure 7. LMK04828 Clock Outputs Tab

11

SLAU616A – January 2015 – Revised January 2016

ADS54J54 Evaluation Module

Copyright © 2015–2016, Texas Instruments Incorporated