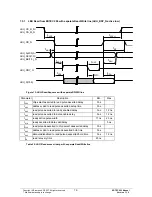

7.5.3

LBU Read from ERTEC 200 with common Read/Write line (LBU_RDY_N active low)

LBU_CS_R_N/

LBU_CS_M_N

LBU_WR

LBU_A(20:0)/

LBU_SEG(1:0)/

LBU_BE(1:0)_N

LBU_RDY

LBU_D(15:0)

t

WCS

t

ACS

t

CRE

t

CDE

t

RTD

t

CDH

t

CAH

t

CWH

t

RAP

t

RR

Figure 15: LBU-Read-Sequence with common RD/WR line

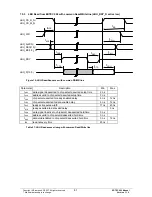

Parameter Description

Min

Max

t

WCS

write signal deasserted to chip select asserted setup time

2 ns

t

ACS

address valid to chip select asserted setup time

0 ns

t

CRE

chip select asserted to ready enabled delay

5 ns

12 ns

t

CDE

chip select asserted to data enable delay

5 ns

12 ns

t

RAP

ready active pulse width

17 ns

23 ns

t

RTD

ready asserted to data valid delay

5 ns

t

CWH

write signal inactive to chip select deasserted hold time

0 ns

t

RAH

address valid to chip select deasserted hold time

0 ns

t

RDH

data valid/enabled to chip select deasserted hold time

0 ns

12 ns

t

RR

read recovery time

25 ns

Table 27: LBU Read access timing with common Read/Write line

Copyright © Siemens AG 2007. All rights reserved.

81

ERTEC 200 Manual

Technical data subject to change

Version 1.1.0