DX-SX1H

– 56 –

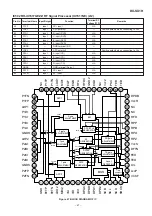

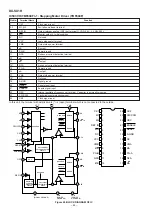

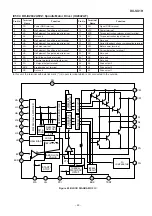

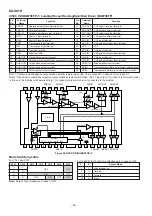

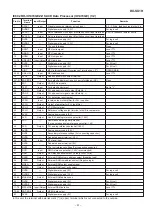

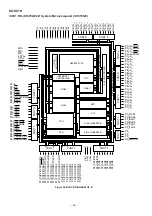

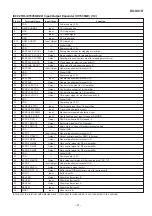

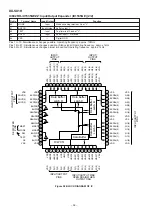

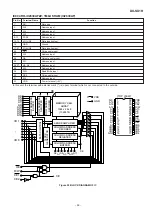

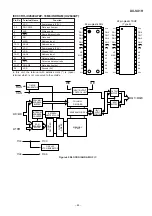

IC801 RH-iX1478GEZZ: System Microcomputer (IX1478GE)

Figure 56 BLOCK DIAGRAM OF IC

MD

2

V

cc

V

cc

V

cc

V

cc

V

cc

V

ss

V

ss

V

ss

V

ss

V

ss

V

ss

V

ss

V

ss

PD

7

/D

15

PD

6

/D

14

PD

5

/D

13

PD

4

/D

12

PD

3

/D

11

PD

2

/D

10

PD

1

/D

9

PD

0

/D

8

PE

7

/D

7

PE

6

/D

6

PE

5

/D

5

PE

4

/D

4

PE

3

/D

3

PE

2

/D

2

PE

1

/D

1

PE

0

/D

0

PA

7

/A

23

/IRQ7

PA

6

/A

22

/IRQ6

MD

1

MD

0

PF

7

/ø

PF

6

/AS

PF

5

/RD

PF

4

/HWR

EXTAL

XTAL

STBY

RES

WDTOVF

NMI

PF

3

/LWR

PF

1

/BACK

PF

0

/BREQ

PG

4

/CS0

PG

3

/CS1

PG

2

/CS2

PG

1

/CS3

PG

0

/CAS

P6

7

/CS7/IRQ3

P6

6

/CS6/IRQ2

P6

5

/IRQ1

P6

4

/IRQ0

P6

3

/TEND1

P6

2

/DREQ1

P6

1

/TEND0/CS5

P6

0

/DREQ0/CS4

PF

2

/LCAS/WAIT/BFEQO

PORT 1

PORT 2

PORT 4

P1

0

/PO8/TIOCA0/DACK0

P1

1

/PO9/TIOCB0/DACK1

P1

2

/PO10/TIOCC0/TCLKA

P1

3

/PO11/TIOCD0/TCLKB

P1

4

/PO12/TIOCA1

P1

5

/PO13/TIOCB1/TCLKC

P1

6

/PO14/TIOCA2

P1

7

/PO15/TIOCB2/TCLKD

P2

0

/PO0/TIOCA3

P2

1

/PO1/TIOCB3

P2

2

/PO2/TIOCC3

P2

3

/PO3/TIOCD3

P2

4

/PO4/TIOCA4

P2

5

/PO5/TIOCB4

P2

6

/PO6/TIOCA5

P2

7

/PO7/TIOCB5

P4

7

/AN7/DA1

P4

6

/AN6/DA0

P4

5

/AN5

P4

4

/AN4

P4

3

/AN3

P4

2

/AN2

P4

1

/AN1

P4

0

/AN0

V

ref

AV

cc

AV

ss

PA

5

/A

21

/IRQ5

PA

4

/A

20

/IRQ4

PA

3

/A

19

PA

2

/A

18

PA

1

/A

17

PA

0

/A

16

PB

7

/A

15

PB

6

/A

14

PB

5

/A

13

PB

4

/A

12

PB

3

/A

11

PB

2

/A

10

PB

1

/A

9

PB

0

/A

8

PC

7

/A

7

PC

6

/A

6

PC

5

/A

5

PC

4

/A

4

PC

3

/A

3

PC

2

/A

2

PC

1

/A

1

PC

0

/A

0

P3

5

/SCK1

P3

4

/SCK0

P3

3

/RxD1

P3

2

/RxD0

P3

1

/TxD1

P3

0

/TxD0

P5

0

P5

1

P5

2

P5

3

/ADTRG

PORT E

PORT D

ROM *

RAM

TPU

PPG

A/D CONVERTER

D/A CONVERTER

SCI

WDT

DMAC

DTC

H8S/2000 CPU

CLOCK

OSCILLA

T

O

R

PORT A

PORT B

PORT C

PORT 3

PORT 5

PORT 6

PORT G

PORT F

INTERRUPT

CONTROLLER

INTERNAL DATA BUS

INTERNAL ADDRESS BUS

BUS CONTROLLER

PERIPHERAL DATA BUS

PERIPHERAL ADDRESS BUS