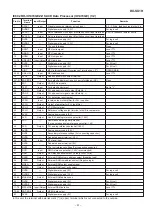

DX-SX1H

– 47 –

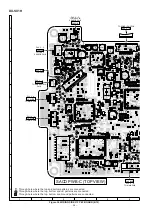

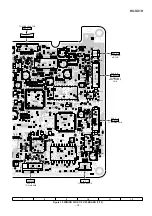

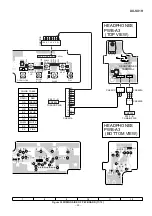

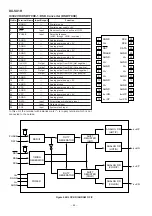

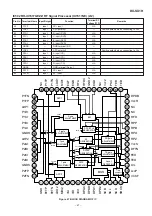

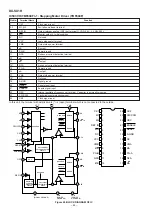

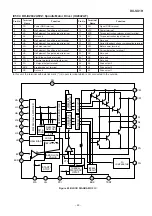

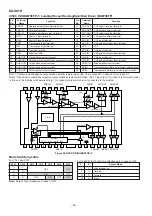

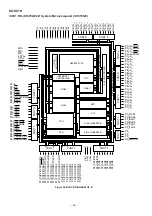

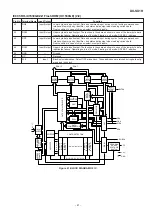

Figure 47 BLOCK DIAGRAM OF IC

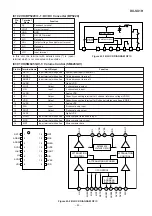

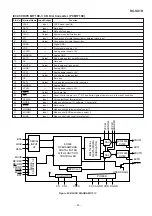

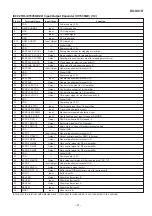

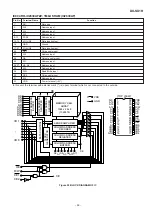

IC502 RH-iX1517GEZZ: RF Signal Processor (IX1517GE) (2/2)

50

P1FP

Input

FE+ input

VrA

51

LDP1

Input

APC polarity 1

—

Positive polarity when connecting to Vcc

52

P1DI

Input

D input (DVD)

VrA

53

P1CI

Input

C input (DVD)

VrA

54

P1BI

Input

B input (DVD)

VrA

55

P1AI

Input

A input (DVD)

VrA

56

GNDR

—

GND terminal (RF)

—

57

LDP2

Input

APC polarity 2

—

Positive polarity when connecting to Vcc

58

P2AI

Input

A input (CD)

VrA

59

P2BI

Input

B input (CD)

VrA

60

P2CI

Input

C input (CD)

VrA

61

P2DI

Input

D input (CD)

VrA

62

GNDS

—

GND terminal (Servo)

—

63

P2FP

Input

FE+ input

VrA

64

P2FN

Input

FE- input

VrA

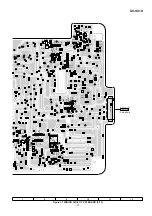

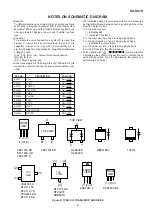

Pin No. Terminal Name Input/Output

Function

Terminal DC

Voltage (TYP.)

Remarks

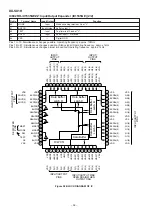

P1FN

P1FP

LDP1

P1DI

P1CI

P1BI

P1AI

GNDR

LDP2

P2AI

P2BI

P2CI

P2DI

GNDS

P2FP

P2FN

DPDB

VccR

NC

NC

RFO

RPP

RPB

RPO

RPZ

VccS

DFTN

FEO

TEO

LVL

LccP

VCKF

NC

P1TP

P1TN

LDO1

MDI1

EQF

EQB

RFA

RFDC

GND2

EQD

NC

Vcc2

PSC

FEB

TEB

GND

P2TP

P2TN

LDO2

MDI2

VrA

VrD

Vdd

DPAC

DPBD

DPD1

DPD2

SCB

SCL

SCD

SRCK

1

2

3

4

5

6

7

8

9 10 11 12 13 14 15 16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

APC1

sel-RF

R-gain

ADJUSTMENT

EQ

F-gain

ADJUSTMENT

F-gain

ADJUSTMENT

RF RIPPLE

GENERATION

FE

GENERATION

DPDTE

GENERATION

FE-gain

ADJUSTMENT

TE-gain

ADJUSTMENT

Level

DETECTION

T-gain

ADJUSTMENT

3BTE

GENERATION

APC2

BUS

sel-PD

sel-PD

sel-PD

mode-TE

sel-FE

sel-IC

sel-TE

sel-DPD

sel-LVL

Time

constant

adjustment