DX-SX1H

– 55 –

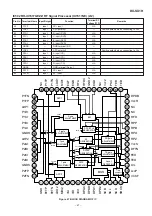

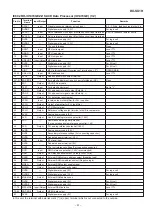

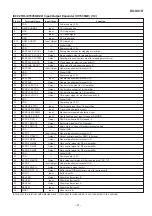

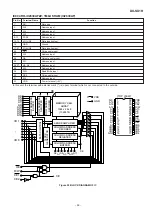

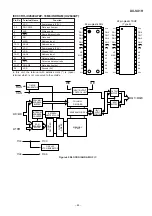

IC606 RH-iX1473GEZZ: Digital Servo (IX1473GE) (3/3)

89

VDD

—

D power terminal

90

VSS

—

Digital ground terminal

91

BUCK

Input

Clock input terminal for microcomputer interface

Schmitt input

92

/CCE

Input

Chip enable signal input terminal for microcomputer interface

Schmitt input

"L": BUS0 to 3 are active.

93

TEST4

Input

Test terminal

Pull-up

Normally open

resistor built in

94

/TSMOD

Input

Local test mode select terminal

Pull-up

resistor built in

95

/RST

Input

Reset signal input terminal

Pull-up

"L" in case of reset

resistor built in

Pull-up resistor

96

TEST0

Input

Test terminal

Pull-up

Normally open

resistor built in

Pull-up resistor

97*

/HSO

Output

Playback speed mode flag output terminal

98*

/UHSO

Output

99

EMPH

Output

Emphasis flag output terminal for sub-code Q data

H: emphasis ON, L: emphasis OFF

Output polarity can be inverted according to commands

100

LRCK

Output

Channel clock (44.1 kHz) output terminal

L channel: L, R channel: H

Output polarity can be inverted according to commands

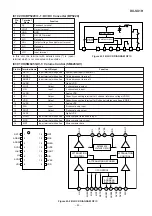

Pin No.

Terminal

Name

Input/Output

Function

Remarks

In this unit, the terminal with asterisk mark (*) is (open) terminal which is not connected to the outside.

/UHSO

H

H

Normal speed playback

H

L

Double speed playback

L

H

4-time speed playback

L

L

8-time speed playback

/HSO

Playback speed

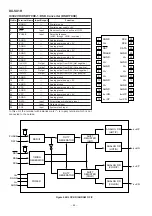

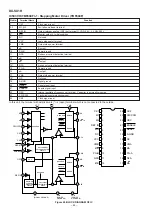

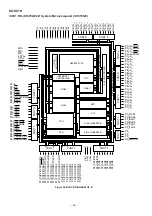

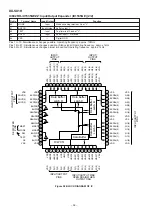

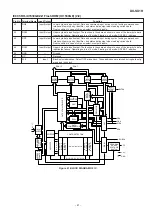

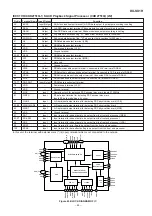

76

DVDD

77

RO

78

DVSS

79

DVR

80

LO

81

DVDD

82

TEST1

83

TEST2

84

TEST3

85

BUS0

86

BUS1

87

BUS2

88

BUS3

89

VDD

90

VSS

91

BUCK

92

/CCE

93

TEST4

94

/TSMOD

95

/RST

96

TEST0

97

/HSO

98

/UHSO

99

EMPH

100

LRCX

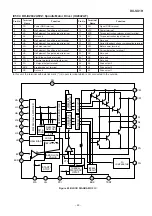

50 DMO

49 FVO

48 FMO

47 TEBC

46 RFGC

45 VREF

44 TRO

43 FOO

42 TEZI

41 TEI

40 TSIN

39 SBAD

38 FEI

37 RFRP

36 RFZI

35 RFCT

34 AVDD

33 RFI

32 SLCO

31 AVSS

30 VCOF

29 VCOREF

28 PVREF

27 LPFO

26 LPFN

1

2

3

4

VSS

BCK

AOUT

5

6

7

8

MBOV

IPF

SBOK

CLCK

9 10 11 12

VDD

VSS

DATA

13

SBSY

14

SPCK

15

SPDA

16

COFS

17

MDNIT

18

VDD

19

TESIOO

20

P2VREF

21

SPDO

22

PDOS

23

PDO

24

TMAXS

25

TMAX

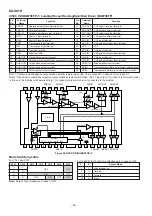

SFSY

DOUT

75 74 73 72

XVDD

XO

XI

71 70 69 68

VDD

PXO

PXI

VSS

67 66 65 64

TESIO1

TESIN

/DACT

63

/DMOUT

62

IO3

61

IO2

60

IO1

59

IO0

58

VSS

57

VDD

56

FLGD

55

FLGC

54

FLGB

53

FLGA

52

SEL

51

2VREF

/CKSE

XVSS

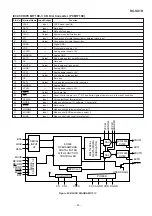

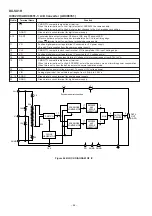

LPF

1BIT

DAC

CLOCK

GENERATOR

1 Gk RAM

CLV SERVO

RAM

ROM

DIGITAL

EQUALIZER

SERVO

CONTROL

PWM

D/A

A/D

+

-

+

-

+

-

+

-

PWM

VCO

PLL TMAX

MICROCONPUTER

INTERFACE

ADDRESS

CIRCUIT

AUTOMATIC

CONTROL

CIRCUIT

CORRECTION

CIRCUIT

EFM DEMODULATION

TO PROTECT

SYNCHRONIZING

SIGNAL

DATA

SLICER

AUDIO

OUTPUT

CIRCUIT

DIGITAL OUT

SUB-CODE

DEMODULATION

CIRCUIT

STATUS

Figure 55 BLOCK DIAGRAM OF IC