18

AK - 45

CHASSIS

• 8-byte Page (1K, 2K), 16-byte Page (4K, 8K, 16K) Write Modes

• Partial Page Writes are Allowed

• Self-timed Write Cycle (10 ms max)

• High-reliability

– Endurance: 1 Million Write Cycles

– Data Retention: 100 Years

• Automotive Grade and Extended Temperature Devices Available

• 8-lead JEDEC SOIC, 8-pin PDIP and 8-lead TSSOP Packages

13.9.3.Pin Configurations

Pin name

Function

A0-A2 Address

Inputs

SDA Serial

Data

SCL

Serial Clock Input

WP Write

Protect

NC No

Connect

13.10.SDA5555

13.10.1.General definition

The SDA55XX is a single chip teletext decoder for decoding World System Teletext data as well as

Video Programming System (VPS), Program Delivery Control (PDC), and Wide Screen Signalling

(WSS) data used for PAL plus transmissions (Line 23). The device also supports Closed caption

acquisition and decoding. The device provides an integrated general-purpose, fully 8051-compatible

Microcontroller with television specific hardware features. Microcontroller has been enhanced to

provide powerful features such as memory banking, data pointers, and additional interrupts etc. The on-

chip display unit for displaying Level 1.5 teletext data can also be used for customer defined on screen

displays. Internal XRAM consists of up to 16 Kbytes. Device has an internal ROM of up to 128 KBytes.

ROMless versions can access up to 1 MByte of external RAM and ROM. The SDA 55XX supports a

wide range of standards including PAL, NTSC and contains a digital slicer for VPS, WSS, PDC, TTX

and Closed Caption, an accelerating acquisition hardware module, a display generator for Level 1.5

TTX data and powerful On screen Display capabilities based on parallel attributes, and Pixel oriented

characters (DRCS).

13.10.2.Features

General

• Feature selection via special function register

• Simultaneous reception of TTX, VPS, PDC, and WSS (line 23)

• Supply Voltage 2.5 and 3.3 V

• ROM version package PSDIP52-2, PMQFP64-1

• Romless version package PMQFP100-2, PLCC84-2

External Crystal and Programmable Clock Speed

• Single external 6MHz crystal, all necessary clocks are generated internally

• CPU clock speed selectable via special function registers.

• Normal Mode 33.33 MHz CPU clock, Power Save mode 8.33 MHz

Microcontroller Features

• 8bit 8051 instruction set compatible CPU.

• 33.33-MHz internal clock (max.)

• 0.360ms (min.) instruction cycle

• Two 16-bit timers

• Watchdog timer

• Capture compare timer for infrared remote control decoding

• Pulse width modulation unit (2 channels 14 bit, 6 channels 8 bit)

• ADC (4 channels, 8 bit)

• UART

Содержание C-2890EES

Страница 7: ...7 C 2890EES CHASSIS LAYOUT Mother Unit CRT Unit Control Panel Unit ...

Страница 69: ...53 AK 45 CHASSIS 14 6 GEOMETRY ADJUSTMENT 4 3 FORMATS 4 3 MODE 16 9 MODE ...

Страница 70: ...54 AK 45 CHASSIS 16 9 FORMATS AUTO MODE ...

Страница 71: ...55 AK 45 CHASSIS REGULAR MODE ...

Страница 72: ...56 AK 45 CHASSIS ZOOM 14 9 MODE ...

Страница 73: ...57 AK 45 CHASSIS ZOOM 16 9 MODE ...

Страница 74: ...58 AK 45 CHASSIS SUBTITLE ZOOM MODE ...

Страница 75: ...59 AK 45 CHASSIS FULL MODE ...

Страница 76: ...60 AK 45 CHASSIS PANORAMIC MODE ...

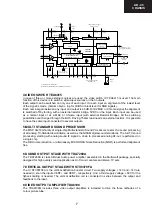

Страница 79: ...63 AK 45 CHASSIS 8 9 10 11 12 13 14 I H G F E D C B A Page 62 16 1 Schematic Diagram of Video IF Circuit ...

Страница 80: ...64 AK 45 CHASSIS 16 2 Schematic Diagram of µ Controller Circuit 1 I H G F E D C B A 2 3 4 5 6 7 ...

Страница 82: ...66 AK 45 CHASSIS 1 I H G F E D C B A 2 3 4 5 6 7 Page 67 16 5 Schematic Diagram of SMPS Circuit ...

Страница 83: ...67 AK 45 CHASSIS 8 9 10 11 12 13 14 I H G F E D C B A Page 66 16 5 Schematic Diagram of SMPS Circuit ...

Страница 84: ...68 AK 45 CHASSIS 1 I H G F E D C B A 2 3 4 5 6 7 Page 69 16 6 Schematic Diagram of Sound Circuit ...

Страница 85: ...69 AK 45 CHASSIS 8 9 10 11 12 13 14 I H G F E D C B A Page 68 16 6 Schematic Diagram of Sound Circuit ...

Страница 86: ...70 AK 45 CHASSIS 1 I H G F E D C B A 2 3 4 5 6 7 16 7 Schematic Diagram of CRT Socket Circuit ...

Страница 87: ...71 AK 45 CHASSIS 8 9 10 11 12 13 14 I H G F E D C B A 16 8 Schematic Diagrams of Control Panel Unit ...

Страница 88: ...72 AK 45 CHASSIS 1 I H G F E D C B A 2 3 4 5 6 7 16 9 Schematic Diagram of Remote Control Circuit ...

Страница 91: ...75 AK 45 CHASSIS Notes ...