PRV-LX10

173

5

6

7

8

5

6

7

8

C

D

F

A

B

E

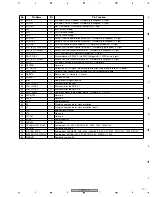

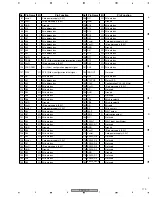

No. Pin Name

I/O

Pin Function

No. Pin Name

I/O

Pin Function

91

V+2_5I

−

+2.5V

136 SDO_LRCK

O

Audio LR clock for SDIOUT

92

V+3_3I

−

+3.3V

137 GNDDI

−

GND

93

GNDDI

−

GND

138 SDI_D0

I

656 video data for SDIIN

94

27MSDO

O

27kHz clock for SDI OUT

139 SDI_D1

I

656 video data for SDIIN

95

L_A0

I

Host address bus

140 LXWE0

I

Host bus read signal

96

L_A1

I

Host address bus

141 SDI_DAI

I

Audio data for SDIIN

97

L_A2

I

Host address bus

142 L_D2

I/O CPU Data/configuration Data

98

L_A3

I

Host address bus

143 V+2_5I

−

+2.5V

99

L_A4

I

Host address bus

144 V+3_3I

−

+3.3V

100 L_A5

I

Host address bus

145 GNDI

−

GND

101 L_A6

I

Host address bus

146 L_D1

I/O CPU Data/configuration Data

102 L_A7

I

Host address bus

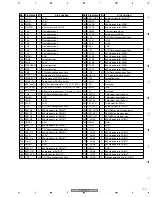

147 SDI_D2

I

656 video data for SDIIN

103 GNDDI

−

GND

148 SDI_D3

I

656 video data for SDIIN

104 DONE

I

for configuration

149 SDI_D4

I

656 video data for SDIIN

105 V+3_3I

−

+3.3V

150 SDI_D5

I

656 video data for SDIIN

106 XPROGRAM

I

for configuration

151 SDI_D6

I

656 video data for SDIIN

107 XINT

I

for configuration

152 SDI_D7

I

656 video data for SDIIN

108 L_D0

I/O CPU Data/configuration Data

153 L_D0

I/O CPU Data/configuration Data

109 APLILIA_DATA

I

Audio data of APLILIA output

154 ENC OK

O

LED port for operation check

110 APLILIA_BCK

I

Audio clock of APLILIA output

155 CCLK

I

for configuration

111 APLILIA_LRCK

I

Audio clock of APLILIA output

156 V+3_3I

−

+3.3V

112 AES_VALID

I

SDI N/PAL distinction signal "L"=PAL, "H"=NTSC

157 TDO

−

Not used

113 SDI_VALID

I

Valid signal of SDI signal "L"= invalid "H"= valid

158 GNDDI

−

GND

114 DINB_EXIST

I

DINB mounting existence signal "L"= nothing, "H" = exists

159 TDI

−

Not used

115 L_D6

I/O CPU Data/configuration Data

160 LXCS40

I

Chip select from the host

116 GNDDI

−

GND

161 LXCS40

I

Chip select from the host

117 V+3_3I

−

+3.3V

162 LXCS56

I

Chip select from the host

118 V+2_5I

−

+2.5V

163 SDI_BCK

I

Audio clock for SDIIN

119 L_D5

I/O CPU Data/configuration Data

164 SDI_LRCK

I

Audio LR clock for SDIIN

120 SDO_D0

O

656 video data for SDIOUT

165 AESI_LRCK

I

AES/EBU audio LR clock input

121 SDO_D1

O

656 video data for SDIOUT

166 AESI_BCK

I

AES/EBU audio clock input

122 SDO_D2

O

656 video data for SDIOUT

167 AESI_DAI

I

AES/EBU audio data input

123 SDO_D3

O

656 video data for SDIOUT

168 F_ADD0

O

656 video data to VAIKILT

124 GNDDI

−

GND

169 GNDDI

−

GND

125 SDO_D4

O

656 video data for SDIOUT

170 V+3_3I

−

+3.3V

126 L_D4

I/O CPU Data/configuration Data

171 V+2_5I

−

+2.5V

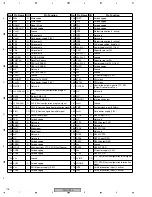

127 SDO_D5

O

656 video data for SDIOUT

172 F_ADD1

O

656 video data to VAIKILT

128 V+2_5I

−

+2.5V

173 F_ADD2

O

656 video data to VAIKILT

129 SDO_D6

O

656 video data for SDIOUT

174 F_ADD3

O

656 video data to VAIKILT

130 V+3_3I

−

+3.3V

175 F_ADD4

O

656 video data to VAIKILT

131 GNDDI

−

GND

176 F_ADD5

O

656 video data to VAIKILT

132 SDO_D7

O

656 video data for SDIOUT

177 GNDDI

−

GND

133 SDO_DAI

O

Audio data for SDIOUT

178 F_ADD6

O

656 video data to VAIKILT

134 SDO_BCK

O

Audio clock for SDIOUT

179 F_ADD7

O

656 video data to VAIKILT

135 L_D3

I/O CPU Data/configuration Data

180 F_NONSI

O

Nonstandard 656 flag to VAIKILT