PDP-501MX, PDP-V501X

63

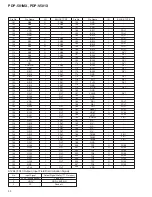

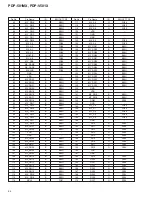

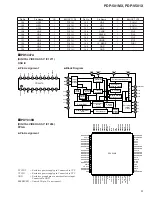

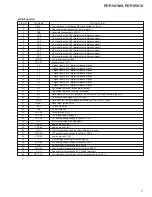

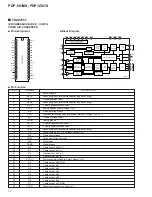

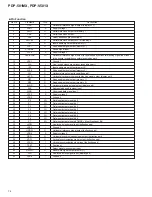

Pin No.

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

Pin Name

PMH

A MUTE

*PNL CE

PLD1 CE

OSD CE

DAC CE

ON MUTE

PLD3 CE

PLD3 RST

GATE CE

AFC SET

EMG S1

EMG S2

FR SEL

*OSD CLR

*RESET2

FAN

TEMP PD

*CB MUTE

EMG

SYNC OX2

SYNC OX1

(VCC)

(VRF)

(AVSS)

TEMP1

TEMP2

TEMP3

TEMP4

TEMP5

I/O

I

O

O

O

O

O

O

O

O

O

O

-

-

O

O

I

O

O

O

O

I

I

-

-

-

I

I

I

I

I

Pin Function

H SYNC when G ON SYNKCOMP SYNC

NOT USED

Enable for panel microprocessor

Enable for PLD1

Enable for OSD

Enable for DAC

NOT USED

-

Enable for PLD3

Reset for PLD3

NOT USED

NOT USED

NOT USED

When free-running is selected: H

When OSD is cleared: L

AC disconnection: L (includes PD detection)

NOT USED

PD output for abnormally high temperature

When ID is set:H

NOT USED

Input for power management

Input for power management

-

-

-

Temperature detection data input. L: Luminance change.

Temperature detection data input. L: POF.

Temperature detection data input (NOT USED).

Temperature detection data input (NOT USED).

Temperature detection data input (NOT USED).

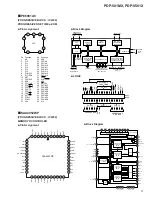

I/O

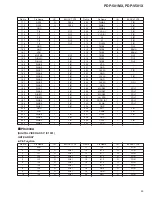

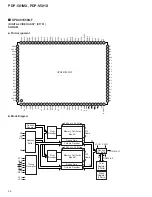

CONTROL

LOGIC

MEMORY

CONTROL

LOGIC

XDEC

HV GENERATOR

EEPROM

ARRAY

PAGE LATCHES

YDEC

SENSE AMP

R/W CONTROL

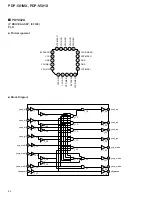

A0--A2 WP

I/O

SCL

V

CC

V

SS

SDA

24LC64(I)SN

V

CC

WP

SCL

SDA

A0

A1

A2

V

SS

1

2

3

4

8

7

6

5

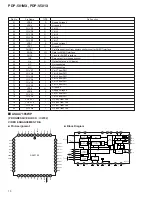

¶

Pin Assignment

7

24LC64(I)SN

(µ-CON ASSY (1/5) : IC3704)

EEPROM

¶

Block Diagram

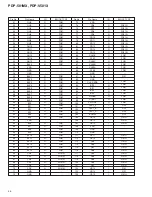

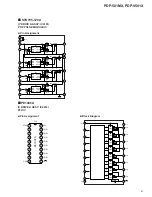

Содержание PDP-501MX

Страница 16: ...PDP 501MX PDP V501X 16 A B C D 1 2 3 4 1 2 3 4 3 3 POWER SUPPLY MODULE 1 2 J 1 2 ...

Страница 17: ...PDP 501MX PDP V501X 17 A B C D 5 6 7 8 5 6 7 8 J 1 2 ...

Страница 18: ...PDP 501MX PDP V501X 18 A B C D 1 2 3 4 1 2 3 4 3 4 POWER SUPPLY MODULE 2 2 J 2 2 ...

Страница 19: ...PDP 501MX PDP V501X 19 A B C D 5 6 7 8 5 6 7 8 J 2 2 ...