PDP-501MX, PDP-V501X

71

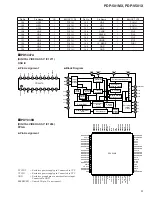

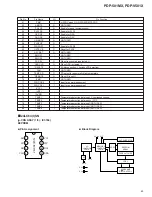

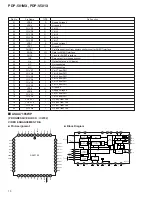

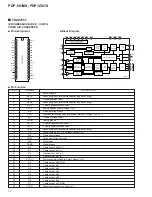

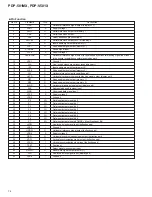

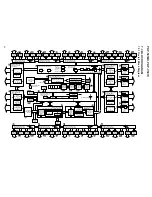

PIN NO.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

PIN NAME

REFL Y

CY

SUB

UV0

UV1

UV2

UV3

UV4

UV5

UV6

UV7

VDD D1

VSS D1

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

AP

SP

MC

LLC

HREF

RESET

SCL

SDA

VSS D2

VDD D2

VDD A1

(R-Y)

VSS A1

VSS A2

(B-Y)

VDD A2

VSS A2

Y

VDD A3

CUR

VDD A4

C UV

REF L UV

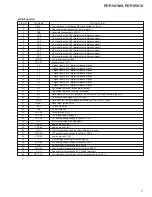

PIN FUNCTION

Low reference of luminance DAC (connected to VSS A1)

Capacitor for luminance DAC (high reference)

Substrate (connected to VSS A1)

UV signal input bit UV7 (digital colour-difference signal)

UV signal input bit UV6 (digital colour-difference signal)

UV signal input bit UV5 (digital colour-difference signal)

UV signal input bit UV4 (digital colour-difference signal)

UV signal input bit UV3 (digital colour-difference signal)

UV signal input bit UV2 (digital colour-difference signal)

UV signal input bit UV1 (digital colour-difference signal)

UV signal input bit UV0 (digital colour-difference signal)

+5V digital supply voltage 1

Digital ground 1(0 V)

Y signal input bit Y7 (digital luminance signal)

Y signal input bit Y6 (digital luminance signal)

Y signal input bit Y5 (digital luminance signal)

Y signal input bit Y4 (digital luminance signal)

Y signal input bit Y3 (digital luminance signal)

Y signal input bit Y2 (digital luminance signal)

Y signal input bit Y1 (digital luminance signal)

Y signal input bit Y0 (digital luminance signal)

Connected to ground (action pin for testing)

Connected to ground (shift pin for testing)

Data cloack CREF(e.g.13.5MHz);at MC=HIGH,the LLC driver-by-two is inactive

Line-locked clock signal(LL27=27MHz)

Data clock for YUV data inputs (for active line 768Y or 640Y long)

Reset input (active LOW)

I

2

C-bus clock line

I

2

c-bus data line

Digital ground 2(0V)

+5V digital supply voltage 2

+5V analog supply voltage for buffer of DAC 1

±(R-Y)output signal (analog signal)

Analog ground 1(0V)

Analog ground 2(0V)

±(B-Y)output signal (analog colour-difference signal)

+5V analog supply voltage for buffer of DAC 2

Analog ground 3 (0V)

Y output signal(analog luminance signal)

+5V analog supply voltage for buffer of DAC 3

Current input for analog output buffers

Supply and reference voltage for the three DAC S

Capacitor for chrominance DAC S(high reference)

Low reference of chrominance DAC S(connected to VSS A1

)

¶

Pin Function

Содержание PDP-501MX

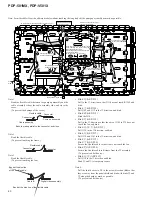

Страница 16: ...PDP 501MX PDP V501X 16 A B C D 1 2 3 4 1 2 3 4 3 3 POWER SUPPLY MODULE 1 2 J 1 2 ...

Страница 17: ...PDP 501MX PDP V501X 17 A B C D 5 6 7 8 5 6 7 8 J 1 2 ...

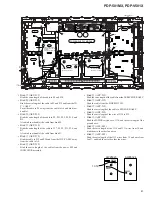

Страница 18: ...PDP 501MX PDP V501X 18 A B C D 1 2 3 4 1 2 3 4 3 4 POWER SUPPLY MODULE 2 2 J 2 2 ...

Страница 19: ...PDP 501MX PDP V501X 19 A B C D 5 6 7 8 5 6 7 8 J 2 2 ...