Memo

ry

Maps

MV

ME

19

7L

E

/D

2

3-

15

3

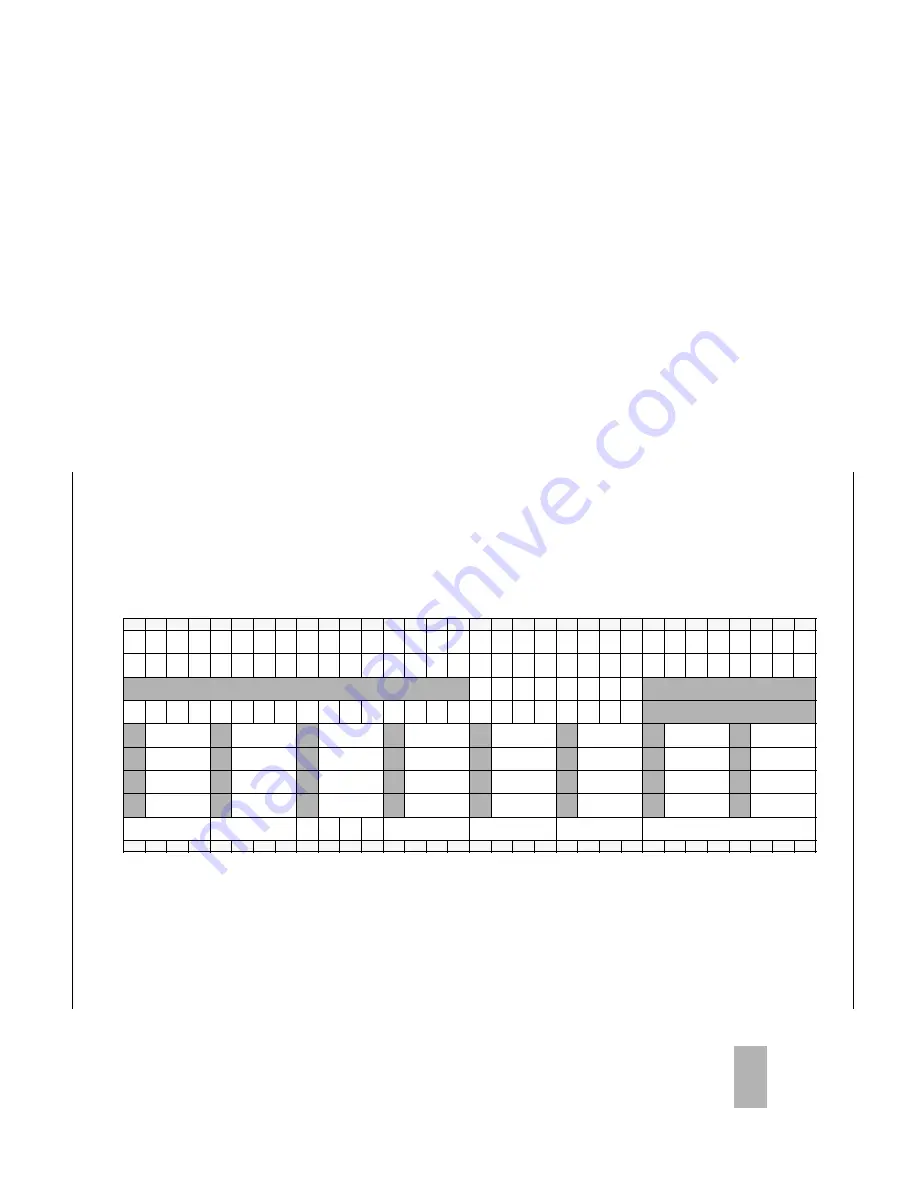

Table 3-6. VMEchip2 Memory Map (Continued)

(Sheet 3 of 4)

VMEchip2 LCSR Base Address = $FFF40000

OFFSET:

D31

D30

D29

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

68

AC

FAIL

IRQ

AB

SW

IRQ

SYS

FAIL

IRQ

MWP

ERR

IRQ

PE

IRQ

IRQ1

EDGE

IRQ

TIC

TIM2

IRQ

TIC

TIM1

IRQ

VME

IACK

IRQ

DMAC

IRQ

GCSR

SIG3

IRQ

GCSR

SIG2

IRQ

GCSR

SIG1

IRQ

GCSR

SIG0

IRQ

GCSR

LM1

IRQ

GCSR

LM0

IRQ

LB

SW7

IRQ

LB

SW6

IRQ

LB

SW5

IRQ

LB

SW4

IRQ

LB

SW3

IRQ

LB

SW2

IRQ

LB

SW1

IRQ

LB

SW0

IRQ

SPARE VME

IRQ7

IRQ

VME

IRQ6

IRQ

VME

IRQ5

IRQ

VME

IRQ4

IRQ

VME

IRQ3

IRQ

VME

IRQ2

IRQ

VME

IRQ1

IRQ

6C

EN

IRQ

31

EN

IRQ

30

EN

IRQ

29

EN

IRQ

28

EN

IRQ

27

EN

IRQ

26

EN

IRQ

25

EN

IRQ

24

EN

IRQ

23

EN

IRQ

22

EN

IRQ

21

EN

IRQ

20

EN

IRQ

19

EN

IRQ

18

EN

IRQ

17

EN

IRQ

16

EN

IRQ

15

EN

IRQ

14

EN

IRQ

13

EN

IRQ

12

EN

IRQ

11

EN

IRQ

10

EN

IRQ

9

EN

IRQ

8

EN

IRQ

7

EN

IRQ

6

EN

IRQ

5

EN

IRQ

4

EN

IRQ

3

EN

IRQ

2

EN

IRQ

1

EN

IRQ

0

70

SET

IRQ

15

SET

IRQ

14

SET

IRQ

13

SET

IRQ

12

SET

IRQ

11

SET

IRQ

10

SET

IRQ

9

SET

IRQ

8

74

CLR

IRQ

31

CLR

IRQ

30

CLR

IRQ

29

CLR

IRQ

28

CLR

IRQ

27

CLR

IRQ

26

CLR

IRQ

25

CLR

IRQ

24

CLR

IRQ

23

CLR

IRQ

22

CLR

IRQ

21

CLR

IRQ

20

CLR

IRQ

19

CLR

IRQ

18

CLR

IRQ

17

CLR

IRQ

16

CLR

IRQ

15

CLR

IRQ

14

CLR

IRQ

13

CLR

IRQ

12

CLR

IRQ

11

CLR

IRQ

10

CLR

IRQ

9

CLR

IRQ

8

78

ACFAIL

IRQ LEVEL

ABORT

IRQ LEVEL

SYSFAIL

IRQ LEVEL

MASTER WRITE

POST ERROR

IRQ LEVEL

PARITY ERROR

IRQ LEVEL

IRQ1

EDGE-SENSITIVE

IRQ LEVEL

TICK TIMER 2

IRQ LEVEL

TICK TIMER 1

IRQ LEVEL

7C

VMEbus

ACKNOWLEDGE

IRQ LEVEL

DMAC

IRQ LEVEL

GCSR

SIG 3

IRQ LEVEL

GCSR

SIG 2

IRQ LEVEL

GCSR

SIG 1

IRQ LEVEL

GCSR

SIG 0

IRQ LEVEL

GCSR

LM 1

IRQ LEVEL

GCSR

LM 0

IRQ LEVEL

80

SW7

IRQ LEVEL

SW6

IRQ LEVEL

SW5

IRQ LEVEL

SW4

IRQ LEVEL

SW3

IRQ LEVEL

SW2

IRQ LEVEL

SW1

IRQ LEVEL

SW0

IRQ LEVEL

84

SPARE

IRQ LEVEL

VMEbus

IRQ7

IRQ LEVEL

VMEbus

IRQ6

IRQ LEVEL

VMEbus

IRQ5

IRQ LEVEL

VMEbus

IRQ4

IRQ LEVEL

VMEbus

IRQ3

IRQ LEVEL

VMEbus

IRQ2

IRQ LEVEL

VMEbus

IRQ1

IRQ LEVEL

88

VECTOR BASE

REGISTER 0

VECTOR BASE

REGISTER 1

MST

IRQ

EN

SYS

FAIL

LEVEL

AC

FAIL

LEVEL

ABORT

LEVEL

GENERAL

PURPOSE

I/O ENABLE

GENERAL

PURPOSE

I/O OUTPUT

GENERAL

PURPOSE

I/O INPUT

GENERAL PURPOSE INPUT

D31

D30

D29

D28

D27

D26

D25

D24

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

LB

= Local Bus

(LB) = Local Bus Slave

LV

= Local Bus to VMEbus

VB

= VMEbus

(VB) = VMEbus Slave

(XX) = Not Used on the MVME197 Series

Содержание MVME197LE

Страница 1: ...MVME197LE Single Board Computer User s Manual MVME197LE D2 ...

Страница 12: ...xii ...

Страница 14: ...xiv ...

Страница 22: ...Hardware Preparation and Installation 2 2 User s Manual 2 ...

Страница 30: ...Hardware Preparation and Installation 2 10 User s Manual 2 ...

Страница 37: ...Memory Maps MVME197LE D2 3 7 3 ...

Страница 40: ...Operating Instructions 3 10 User s Manual 3 ...

Страница 42: ...Operating Instructions 3 12 User s Manual 3 ...

Страница 44: ...Operating Instructions 3 14 User s Manual 3 ...

Страница 46: ...Operating Instructions 3 16 User s Manual 3 ...

Страница 48: ...Operating Instructions 3 18 User s Manual 3 ...

Страница 60: ...Functional Description 4 2 User s Manual 4 ...

Страница 68: ...Functional Description 4 10 User s Manual 4 ...

Страница 78: ...Index IN 4 User s Manual I N D E X ...