O

p

erating In

st

ruction

s

3-

8

Us

er’s M

an

u

al

3

Table 3-4. ECDM CSR Register Memory Map

Sub-System Memory CSR Base Address = $FFF01000

Offset/Register:

ECDM0

ECDM1

ECDM2

ECDM3

ADDR/REGISTER ADDR/REGISTER ADDR/REGISTER ADDR/REGISTER ADDR/REGISTER ADDR/REGISTER ADDR/REGISTER ADDR/REGISTER

00 / MEMCON0

01 / ECDMID0

02 / MEMCON1

03 / ECDMID1

04 / MEMCON2

05 / ECDMID2

06 / MEMCON3

07 / ECDMID3

08 / SYNSTAT0

09 / ERSTAT0

0A / SYNSTAT1

0B / ERSTAT1

0C / SYNSTAT2

0D / ERSTAT2

0E / SYNSTAT3

0F / ERSTAT3

10 / I2CON0

11 / I2STAT0

12 / I2CON1

13 / I2STAT1

14 / I2CON2

15 / I2STAT2

16 / I2CON3

17 / I2STAT3

18 / I2DATA0

19 / I2ADDR0

1A / I2DATA1

1B / I2ADDR1

1C / I2DATA2

1D / I2ADDR2

1E / I2DATA3

1F / I2ADDR3

D64

D56

D55

D48

D47

D40

D39

D32

D31

D24

D23

D16

D15

D8

D7

D0

ECDM register map of four ECDM devices in a 64-bit system. The byte offset address is shown next to each register.

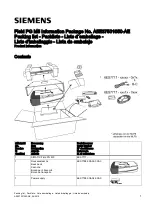

Содержание MVME197LE

Страница 1: ...MVME197LE Single Board Computer User s Manual MVME197LE D2 ...

Страница 12: ...xii ...

Страница 14: ...xiv ...

Страница 22: ...Hardware Preparation and Installation 2 2 User s Manual 2 ...

Страница 30: ...Hardware Preparation and Installation 2 10 User s Manual 2 ...

Страница 37: ...Memory Maps MVME197LE D2 3 7 3 ...

Страница 40: ...Operating Instructions 3 10 User s Manual 3 ...

Страница 42: ...Operating Instructions 3 12 User s Manual 3 ...

Страница 44: ...Operating Instructions 3 14 User s Manual 3 ...

Страница 46: ...Operating Instructions 3 16 User s Manual 3 ...

Страница 48: ...Operating Instructions 3 18 User s Manual 3 ...

Страница 60: ...Functional Description 4 2 User s Manual 4 ...

Страница 68: ...Functional Description 4 10 User s Manual 4 ...

Страница 78: ...Index IN 4 User s Manual I N D E X ...