MOTOROLA

DSP96002 USER’S MANUAL

9 - 3

If the Host Interface flag HF1 is set, the bootstrap program assumes that the external host processor

is a 32-bit wide source which will supply up to 1,024 32-bit words to load into the program RAM.

The external host processor may terminate the bootstrap program by setting the Host Interface flag

HF0.

5.

Enter Mode 0 or 1 by writing to the OMR. This action will begin a timed delay to remove the

bootstrap ROM from the program memory map.

6.

This timed delay is exactly timed to allow the boot program to execute a NOP then a JMP to

location $00000000 and begin execution of the user’s program.

The user may also select a bootstrap mode by writing into the OMR. This technique allows the

DSP96002 programmer to re-boot his system. From any operating mode, the user may program the

OMR to the required bootstrap mode. This begins a timed delay to map the bootstrap ROM into the

program address space. This timed delay is exactly timed to allow the programmer to execute a

NOP then a JMP to bootstrap ROM location $00000000 and begin the bootstrap process described

above in steps 1 to 6.

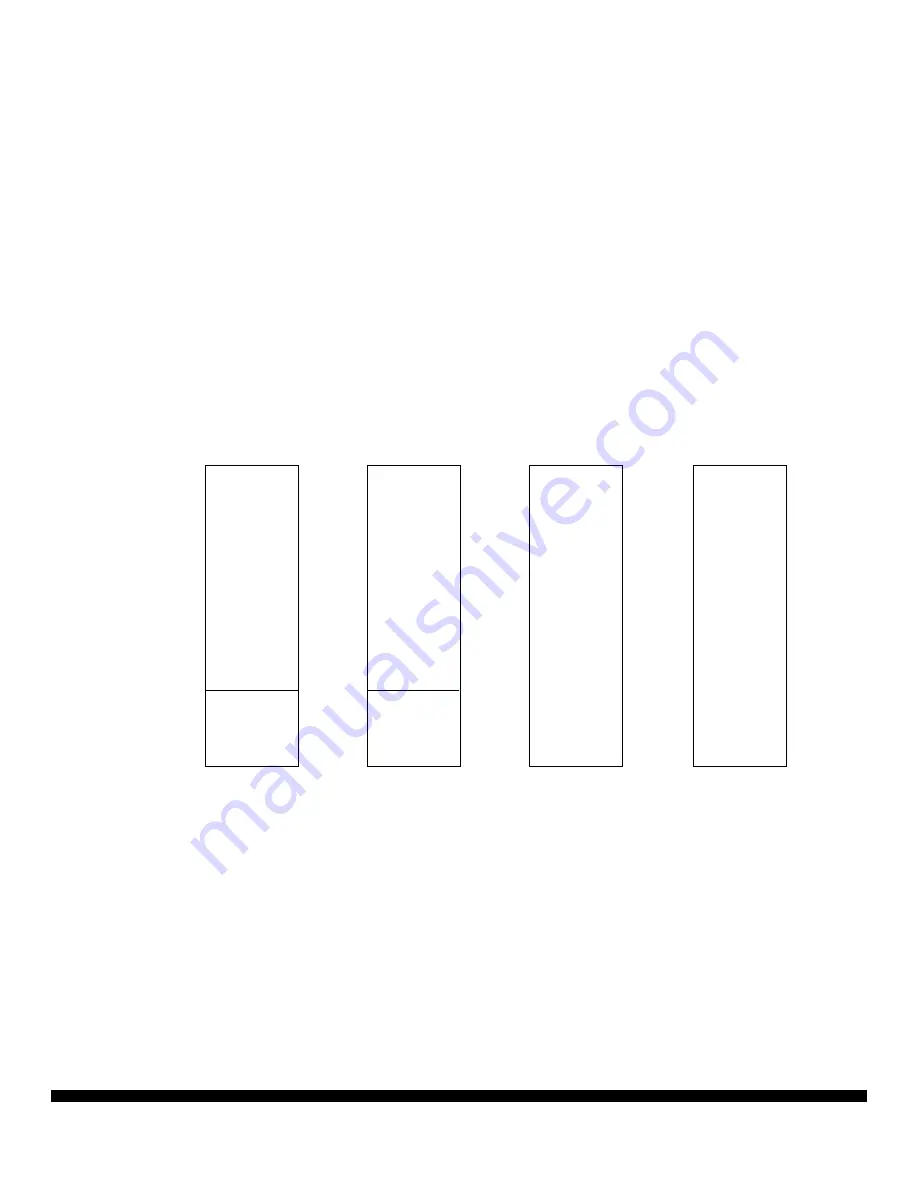

Mode 0 Mode 1 Mode 2 Mode 3

$FFFF- $FFFF- $FFFF- $FFFF-

FFFF FFFF FFFF FFFF

External External External External

Program Program Program Program

Memory Memory Memory Memory

$0000- $0000-

03FF Internal 03FF Internal

Program Program

RAM RAM

$0000- $0000- $0000- $0000-

0000 0000 0000 0000

HW Reset:

$FFFFFFFE $FFFFFFFE $00000000 $00000000

Port A Port B Port A Port B

Figure 9-2. DSP96002 Program Memory Maps

Содержание DSP96002

Страница 3: ...1 2 DSP96002 USER S MANUAL MOTOROLA ...

Страница 38: ...MOTOROLA DSP96002 USER S MANUAL 3 15 Figure 3 4 Modulo Arithmetic Unit Block Diagram ...

Страница 39: ...3 16 DSP96002 USER S MANUAL MOTOROLA ...

Страница 53: ...4 14 DSP96002 USER S MANUAL MOTOROLA ...

Страница 76: ...MOTOROLA DSP96002 USER S MANUAL 5 23 Figure 5 8 Address Modifier Summary ...

Страница 86: ...6 10 DSP96002 USER S MANUAL MOTOROLA ...

Страница 101: ...MOTOROLA DSP96002 USER S MANUAL 7 15 Figure 7 9 HI Block Diagram One Port ...

Страница 140: ...7 54 DSP96002 USER S MANUAL MOTOROLA ...

Страница 166: ...9 10 DSP96002 USER S MANUAL MOTOROLA ...

Страница 181: ...MOTOROLA DSP96002 USER S MANUAL 10 15 Figure 10 8 Program Address Bus FIFO ...

Страница 336: ...A 148 DSP96002 USER S MANUAL MOTOROLA FMPY S2 S1 D1 FSUB S S3 D2 move syntax see the MOVE instruction de scription ...

Страница 337: ...MOTOROLA DSP96002 USER S MANUAL A 149 ...

Страница 404: ...A 216 DSP96002 USER S MANUAL MOTOROLA PC xxxx D ...

Страница 460: ...A 272 DSP96002 USER S MANUAL MOTOROLA SIOP Not affected ...

Страница 484: ...A 296 DSP96002 USER S MANUAL MOTOROLA SSH PC SSL SR SP 1 SP ...

Страница 519: ...MOTOROLA DSP96002 USER S MANUAL A 331 ...

Страница 580: ...MOTOROLA DSP96002 USER S MANUAL B 61 X Memory Y Memory n0 3 r0 x0 Xmin r4 y0 Xmax z0 Ymin x1 Ymax y1 Zmin z1 Zmax ...

Страница 718: ...MOTOROLA DSP96002 USER S MANUAL B 199 ...

Страница 871: ... MOTOROLA INC 1994 MOTOROLA TECHNICAL DATA SEMICONDUCTOR M Addendum ...

Страница 888: ...MOTOROLA INDEX 1 INDEX ...

Страница 889: ......