MAX32660 User Guide

Maxim Integrated

Page 148 of 195

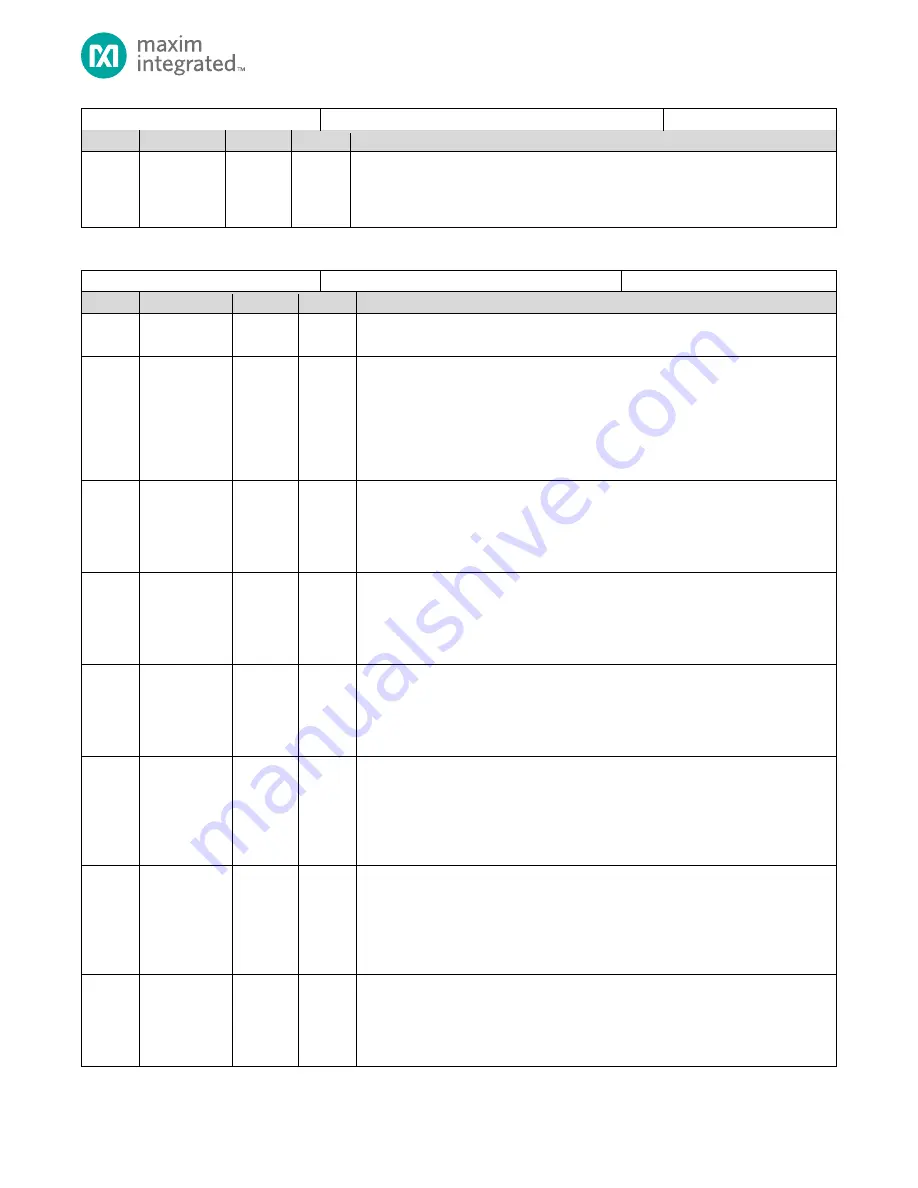

I

2

C Status Register

I2Cn_STATUS

[0x0004]

Bits

Name

Access

Reset

Description

0

busy

RO

0

Bus Busy

If set, the I

2

C bus is active.

0: Bus is idle

1: Bus is busy

Table 12-6: I

2

C Interrupt Status Flags Registers 0

I

2

C Interrupt Status Flags 0 Register

I2Cn_INTFL0

[0x0008]

Bits

Name

Access

Reset

Description

31:16

-

R/W

0

Reserved for Future Use

Do not modify this field.

15

txloi

R/W1C

0

TX FIFO Locked Interrupt Flag

If set, the TX FIFO is locked and writes to the TX FIFO are ignored. This field is set to 1

by hardware to prevent stale data from being transmitted from the TX FIFO. When

set, the TX FIFO is automatically flushed. Writes to the TX FIFO are ignored until this

flag is cleared. Write 1 to clear.

0: TX FIFO not locked.

1: TX FIFO is locked and all writes to the TX FIFO are ignored.

14

stoperi

R/W1C

0

Out of Sequence STOP Interrupt Flag

This flag is set if a STOP condition occurs on the I

2

C Bus out of expected sequence.

Write 1 to clear this field. Writing 0 has no effect.

0: Error condition has not occurred.

1: Out of sequence STOP condition occurred.

13

strteri

R/W1C

0

Out of Sequence START Interrupt Flag

This flag is set if a START condition occurs on the I

2

C Bus out of expected sequence.

Write 1 to clear this field. Writing 0 has no effect.

0: Error condition has not occurred.

1: Out of sequence START condition occurred.

12

dnreri

R/W1C

0

Slave Mode Do Not Respond Interrupt Flag

This occurs if an address match is made, but the TX FIFO or RX FIFO is not ready.

Write 1 to clear this field. Writing 0 has no effect.

0: Error condition has not occurred.

1: I

2

C address match has occurred and either the TX or RX FIFO is not configured.

11

dateri

R/W1C

0

Master Mode: Data NACK from External Slave Interrupt Flag

This flag is set by hardware if a NACK is received from a slave on the I

2

C bus. This flag

is only valid if the I2Cn peripheral is configured for Master Mode operation. Write 1

to clear. Write 0 has no effect.

0: Error condition has not occurred.

1: Data NACK received from a slave.

10

adreri

R/W1C

0

Master Mode: Address NACK from Slave Error Flag

This flag is set by hardware if an Address NACK is received from a slave on the I

2

C bus.

This flag is only valid if the I2Cn peripheral is configured for Master Mode operation.

Write 1 to clear. Write 0 has no effect.

0: Error condition has not occurred.

1: Address NACK received from a slave.

9

toeri

R/ W1C

0

Timeout Error Interrupt Flag

This occurs when this device holds SCL low longer than the programmed timeout

value. Applies to both Master and Slave Mode. Write 1 to clear. Write 0 has no effect.

0: Timeout error has not occurred.

1: Timeout error occurred.

Содержание MAX32660

Страница 4: ...MAX32660 User Guide Maxim Integrated Page 4 of 195 8 UART 84 9 Real Time Clock RTC 96 10 Timers 105...

Страница 7: ...MAX32660 User Guide Maxim Integrated Page 7 of 195 15 Trademarks 195 16 Revision History 195...

Страница 14: ...MAX32660 User Guide Maxim Integrated Page 14 of 195 Figure 2 1 MAX32660 High Level Block Diagram...