LTC3810-5

24

38105fd

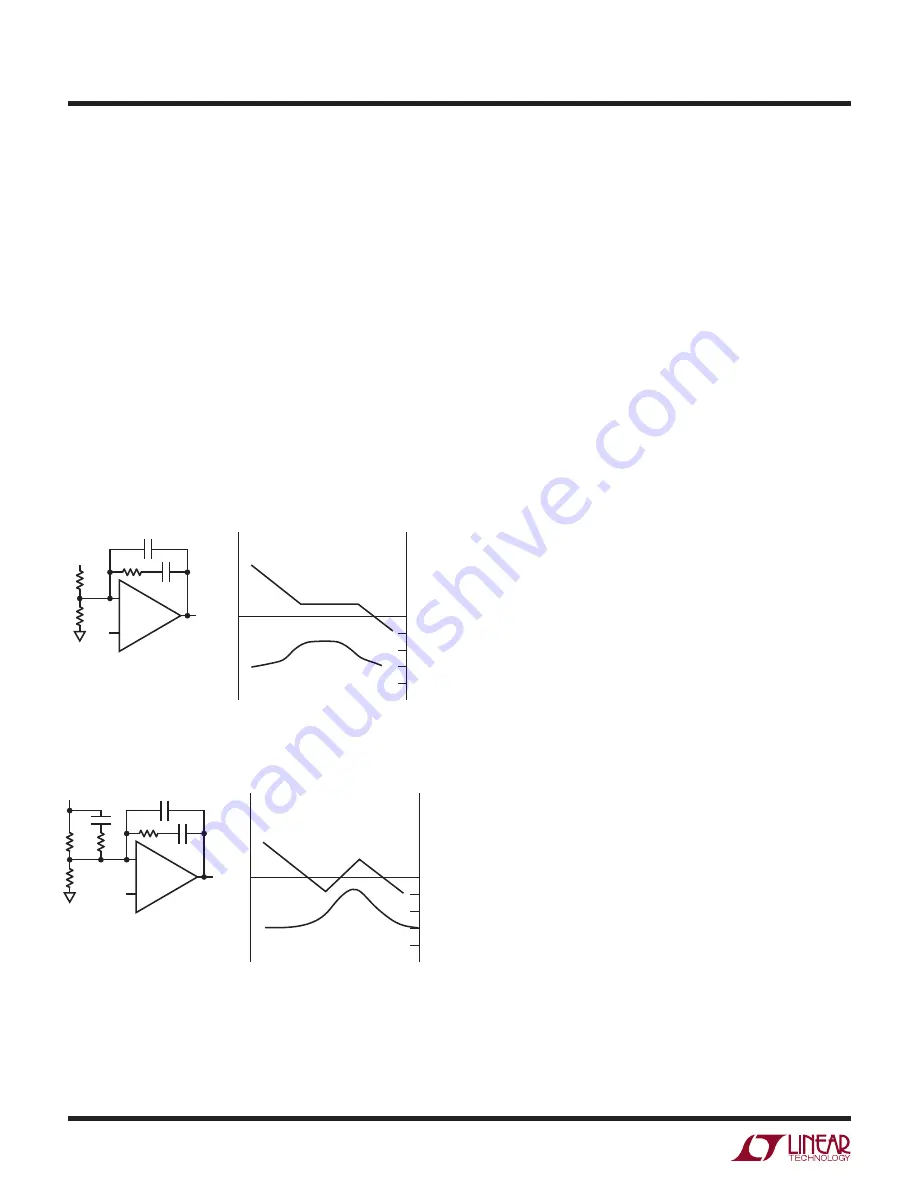

Figure 11. Type 2 Schematic and Transfer Function

requirement of the compensation will be to guarantee that

the gain is below zero at frequencies above f

SW

/4. If the

ESR zero is above the crossover frequency, the feedback

amplifier will probably be required to provide phase boost.

For most LTC3810-5 applications, Type 2 compensation will

provide enough phase boost; however some applications

where high bandwidth is required with low ESR ceramics

and lots of bulk capacitance, Type 3 compensation may

be necessary to provide additional phase boost.

The two types of compensation networks, “Type 2” and

“Type 3” are shown in Figures 11 and 12. When compo-

nent values are chosen properly, these networks provide

a “phase bump” at the crossover frequency. Type 2 uses

a single pole-zero pair to provide up to about 60° of phase

boost while Type 3 uses two poles and two zeros to provide

up to 150° of phase boost.

Figure 12. Type 3 Schematic and Transfer Function

Feedback Component Selection

Selecting the R and C values for a typical Type 2 or Type 3

loop is a nontrivial task. The applications shown in this

data sheet show typical values, optimized for the power

components shown. They should give acceptable perfor-

mance with similar power components, but can be way off if

even one major power component is changed significantly.

Applications that require optimized transient response will

require recalculation of the compensation values specifically

for the circuit in question. The underlying mathematics are

complex, but the component values can be calculated in

a straightforward manner if we know the gain and phase

of the modulator at the crossover frequency.

Modulator gain and phase can be obtained in one of

three ways: measured directly from a breadboard, or if

the appropriate parasitic values are known, simulated or

generated from the modulator transfer function. Mea-

surement will give more accurate results, but simulation

or transfer function can often get close enough to give

a working system. To measure the modulator gain and

phase directly, wire up a breadboard with an LTC3810-5

and the actual MOSFETs, inductor and input and output

capacitors that the final design will use. This breadboard

should use appropriate construction techniques for high

speed analog circuitry: bypass capacitors located close

to the LTC3810-5, no long wires connecting components,

appropriately sized ground returns, etc. Wire the feedback

amplifier with a 0.1µF feedback capacitor from I

TH

to FB

and a 10k to 100k resistor from V

OUT

to FB. Choose the

bias resistor (R

FB2

) as required to set the desired output

voltage. Disconnect R

FB2

from ground and connect it to

a signal generator or to the source output of a network

analyzer to inject a test signal into the loop. Measure the

gain and phase from the I

TH

pin to the output node at the

positive terminal of the output capacitor. Make sure the

analyzer’s input is AC coupled so that the DC voltages

present at both the I

TH

and V

OUT

nodes don’t corrupt the

measurements or damage the analyzer.

If breadboard measurement is not practical, a SPICE

simulation can be used to generate approximate gain/

phase curves. Plug the expected capacitor, inductor and

MOSFET values into the following SPICE deck and gener-

ate an AC plot of V

OUT

/V

ITH

with gain in dB and phase in

applicaTions inForMaTion

GAIN (dB)

38105 F11

0

PHASE

–6dB/OCT

–6dB/OCT

GAIN

PHASE (DEG)

FREQ

–90

–180

–270

–360

R

FB2

V

REF

R

FB1

R2

FB

C2

IN

OUT

+

–

C1

GAIN (dB)

38105 F12

0

PHASE

–6dB/OCT

+6dB/OCT

–6dB/OCT

GAIN

PHASE (DEG)

FREQ

–90

–180

–270

–360

V

REF

R2

FB

C2

IN

OUT

+

–

C1

C3

R3

R

FB2

R

FB1