LMS6002D Quick Starter Manual for Evaluation Board

89 |

P a g e

© Copyright Lime Microsystems

Rev: 2.2

Last modified: 03/05/2012

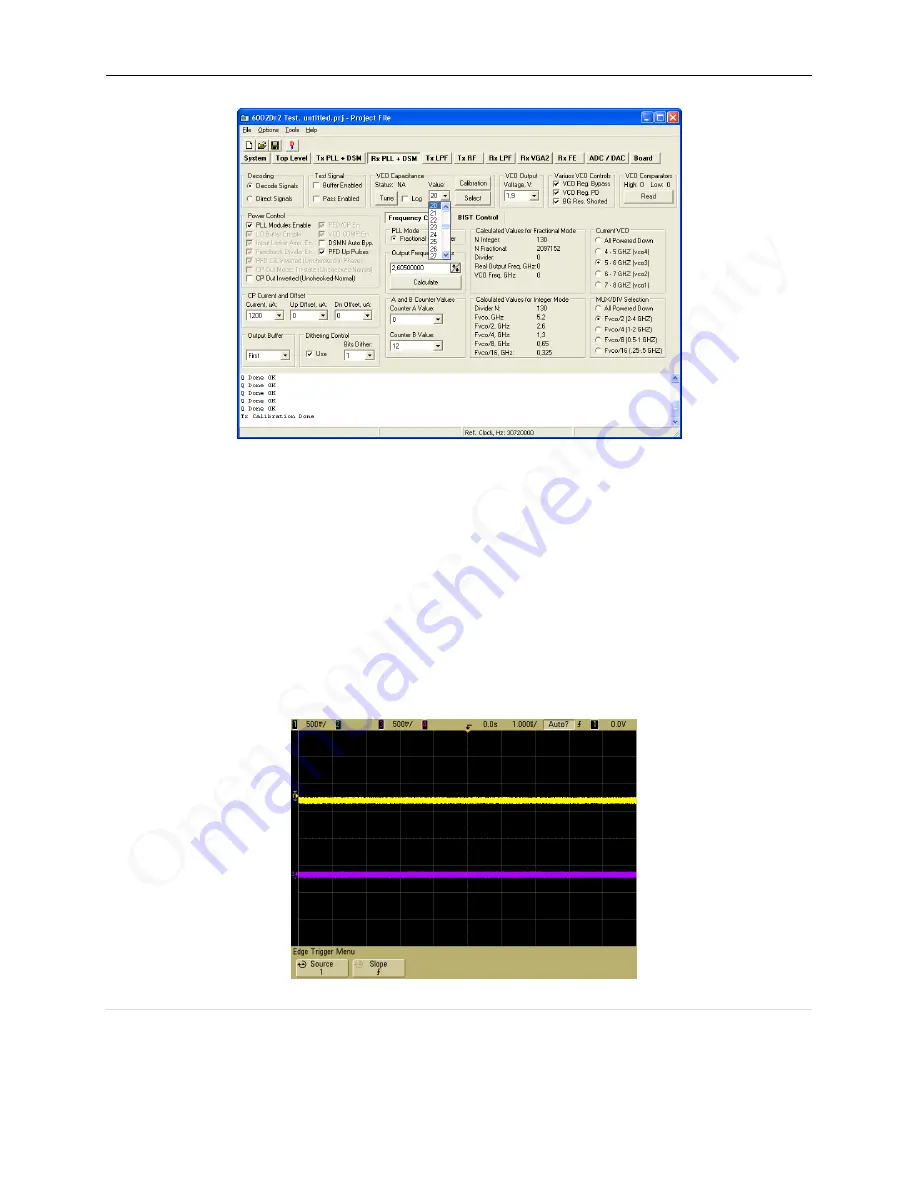

Figure 88 Rx PLL VCO capacitance

By clicking on the number in the VCO capacitance control the drop down box is released, a new

number can be selected from this box, or by clicking again in the box the drop down menu will

collapse but the box remains highlighted. The up/down arrows on the keyboard can now be used

to cycle through the capacitance values. As soon as the number is change it is downloaded to the

LMS6002D so scrolling through and observing the effect is quite fast.

There are 3 types of display on the scope that can occur when doing this testing.

1.

No receive baseband output as shown below. This implies the synthesizer is not locked so

there is no output from the down conversion in the baseband bandwidth.

Figure 89 No Receive Baseband Output