LMS6002D Quick Starter Manual for Evaluation Board

43 |

P a g e

© Copyright Lime Microsystems

Rev: 2.2

Last modified: 03/05/2012

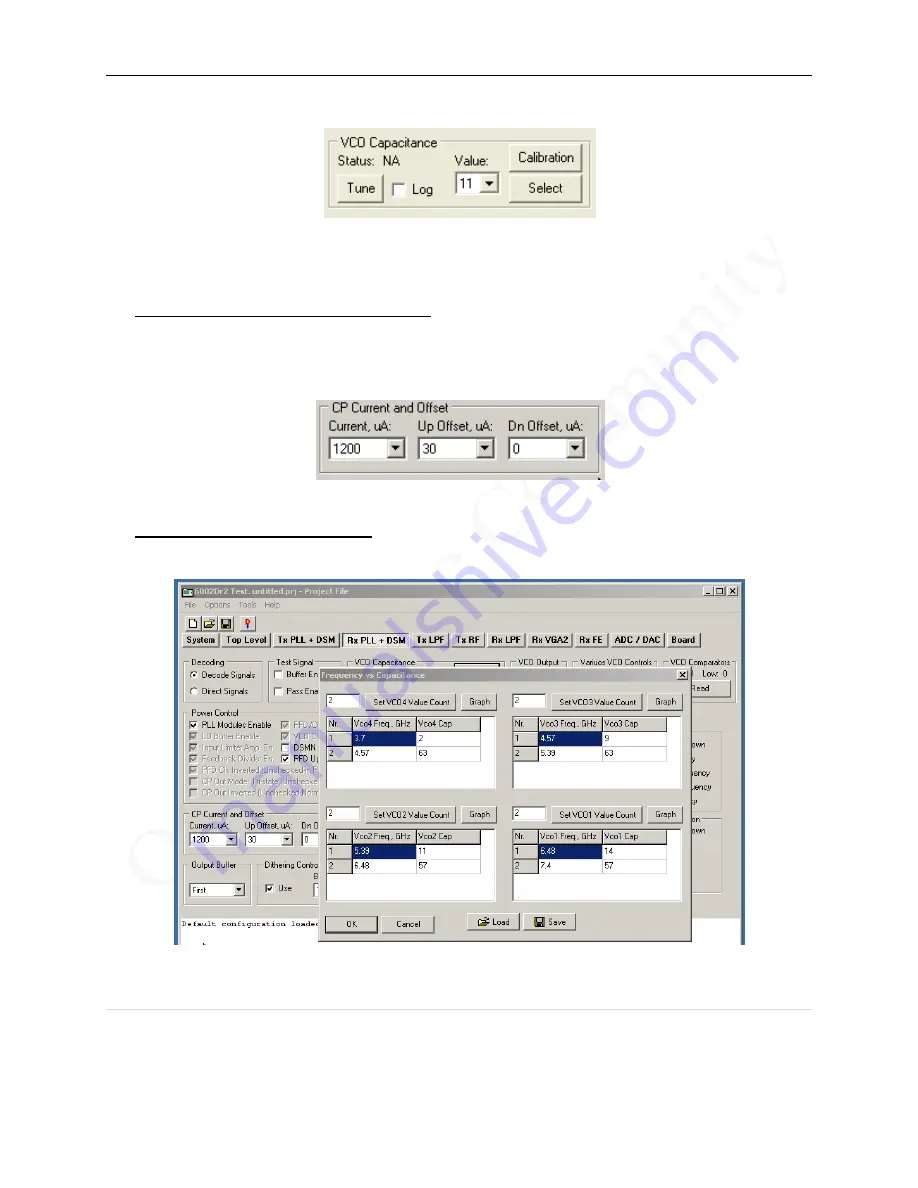

Figure 38 VCO Capacitance

Use of the

‘Calibration’

button is described at the end of this section.

Charge Pump(CP) Current and Offset

CP Current and Offset is set based on the selected loop filter and loop BW. For the

recommended loop filter (implemented on the evaluation board). Current should be 1200uA

and Up Offset 30uA, as shown.

Figure 39 CP Current and Offset

PLL Calibration Data and File

Press the

‘Calibration’

button to enter the Frequency vs Capacitance calibration table data.

Figure 40 Frequency vs capacitance calibration table data