Keithley DAS-1700 Series

Using the DAS-1700 Series with DriverLINX

•

101

Counter/Timer Subsystem

The DAS-1700 Series has counter/timers for analog input/output pacing only. All

models use an Intel 8254 Programmable Interval Timer that consists of 3 internal 16-

bit counters, Counter 0, Counter 1, and Counter 2.

For analog input pacing, the DAS-1700 boards operate Counters 1 and 2 in a fixed

divider, 32-bit configuration. The input of Counter 1 connects to a 5 MHz crystal

oscillator and the output of Counter 1 connects to the input of Counter 2.

The DAS-1700 uses Counter 0 for trigger delay and its input, output, and gate control

are not available.

DriverLINX implements only one Logical Counter, Logical Channel 0, which

corresponds to the internal Analog Input pacing clock (8254 counters 1 and 2). You

can use Logical Channel 0 to pace Analog Output or Digital I/O tasks indirectly

through hardware interrupts.

The DAS-1700AO has an additional counter/timer for supporting timed Analog

Output tasks in hardware. DriverLINX implements two Logical Counters in this case,

Logical Counter 0, which corresponds to the internal Analog Input pacing clock, and

Logical Counter 1, which corresponds to the internal Analog Output pacing clock.

See “Counter/Timer Subsystem Signals” on page 36 for connection details.

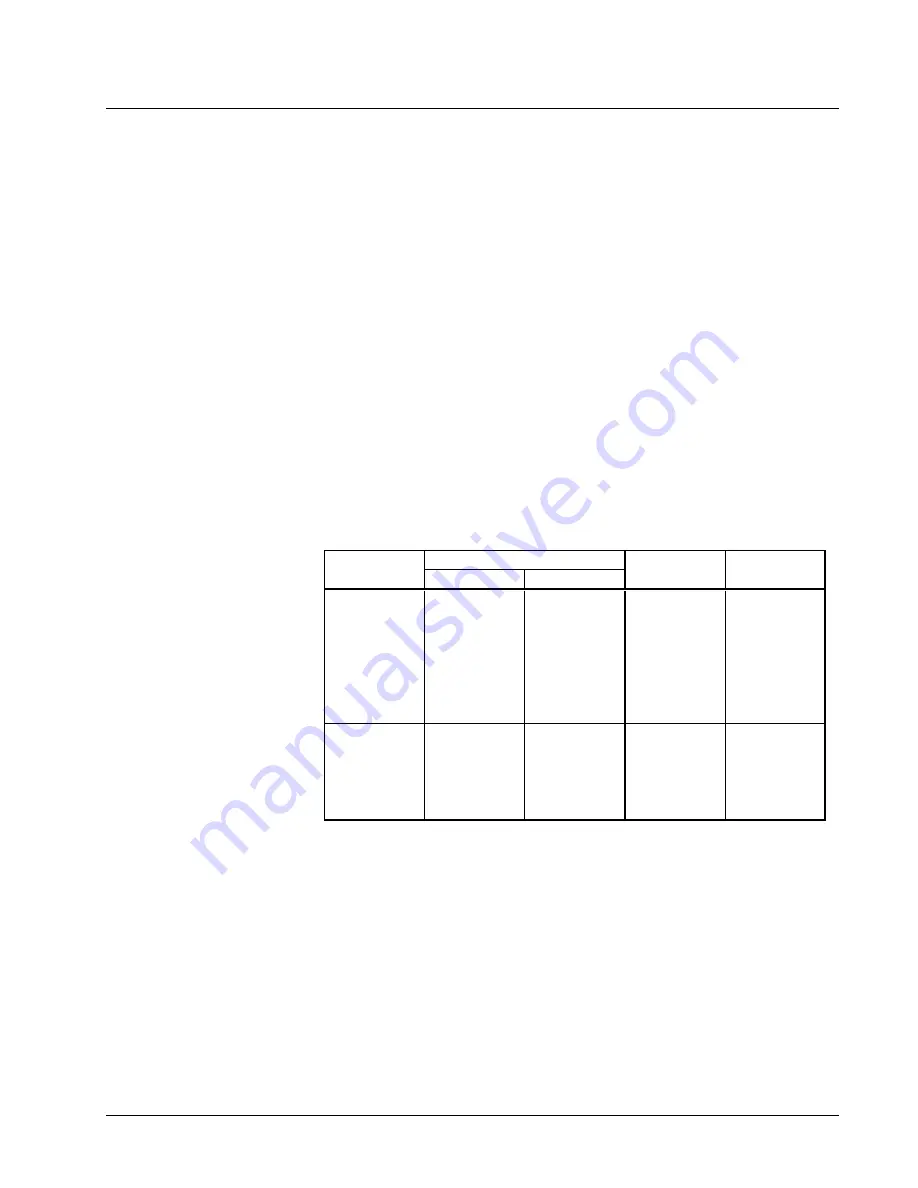

The following table lists the Counter/Timer Subsystem’s Logical Channels and shows

their allowable clock sources, modes and gates:

Logical

Clocks

Modes

Gates

Channels

Source

Tic Period

0

Internal

0.2 µs

Rate Gen

Enabled

AI, DI and DO External

Burst Gen

Disabled

Pacing E

No

Connect

External-

Low Level

Low Edge

High Level

High Edge

1

Internal

0.2 µs

Rate Gen

Enabled

AO Pacing

External

Disabled

(AO models

E

No Connect

only)

External-

Low Level

High Level

Counter/Timer Subsystem Logical Channels and Allowed Clocks, Modes and Gates.

Gate Settings

The Gate setting specifies how the TGIN signal affects the operation of the internal

or external clock. Valid settings are Enabled, Disabled, No Connect, High Level,

Low Level, Low Edge and High Edge.

•

Enabled selects the gate’s default enabled mode. On the DAS-1700

Series this is High Level Enabled.

•

Disabled allows the clock to pace samples independently of the gate

signal.

StockCheck.com