8

603 Hardware Specifications, REV 2

Preliminary—Subject to Change without Notice

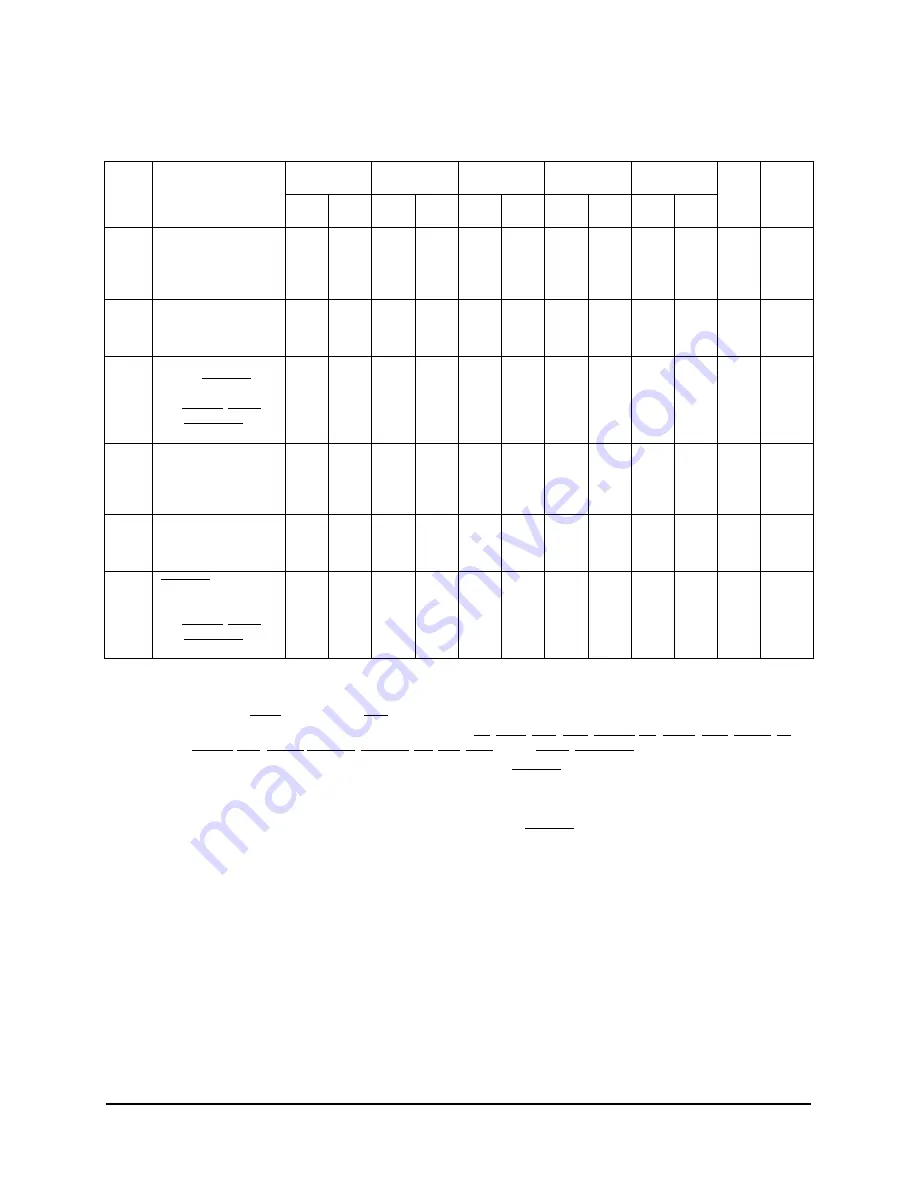

Table 6. Input AC Timing Specifications

Vdd = 3.3

±

5% V dc, GND = 0 V dc

,

0

≤

T

J

≤

105

°

C

Num

Characteristic

25 MHz

33.33 MHz

40 MHz

50 MHz

66.67 MHz

Unit

Notes

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

10a

Address/data/transfer

attribute inputs valid

to SYSCLK (input

setup)

4.5

—

4.0

—

3.5

—

3.0

—

2.5

—

ns

2

10b

All other inputs valid

to SYSCLK (input

setup)

6.5

—

6.0

—

5.5

—

5.0

—

4.5

—

ns

3

10c

Mode select inputs

valid to HRESET

(input setup)

(for DRTRY, QACK

and TLBISYNC)

8 *

t

sys

—

8 *

t

sys

—

8 *

t

sys

—

8 *

t

sys

—

8 *

t

sys

—

ns

4,5,

6,7

11a

SYSCLK to

address/data/transfer

attribute inputs

invalid (input hold)

1.0

—

1.0

—

1.0

—

1.0

—

1.0

—

ns

2

11b

SYSCLK to all other

inputs invalid (input

hold)

1.0

—

1.0

—

1.0

—

1.0

—

1.0

—

ns

3

11c

HRESET to mode

select inputs invalid

(input hold)

(for DRTRY, QACK,

and TLBISYNC)

0

—

0

—

0

—

0

—

0

—

ns

4,6,7

Notes: 1. All input specifications are measured from the TTL level (0.8 or 2.0 V) of the signal in question to the 1.4 V of the

rising edge of the input SYSCLK. Both input and output timings are measured at the pin. See Figure 2.

2. Address/data/transfer attribute input signals are composed of the following: A0–A31, AP0–AP3, TT0–TT4,

TC0–TC1, TBST, TSIZ0–TSIZ2, GBL, DH0–DH31, DL0–DL31, DP0–DP7.

3. All other input signals are composed of the following: TS, XATS, ABB, DBB, ARTRY, BG, AACK, DBG, DBWO, TA,

DRTRY, TEA, DBDIS,HRESET, SRESET, INT, SMI, MCP, TBEN, QACK, TLBISYNC.

4. The setup and hold time is with respect to the rising edge of HRESET. See Figure 3.

5. t

SYS

is the period of the external clock (SYSCLK) in nanoseconds.

6. These values are guaranteed by design, and are not tested.

7. This specification is for configuration mode only. Also note that HRESET must be held asserted for a minimum of

255 bus clocks after the PLL relock time (100

µ

s) during the power-on reset sequence.