Rev. 1.20

16

October 28, 2020

BC45B4523

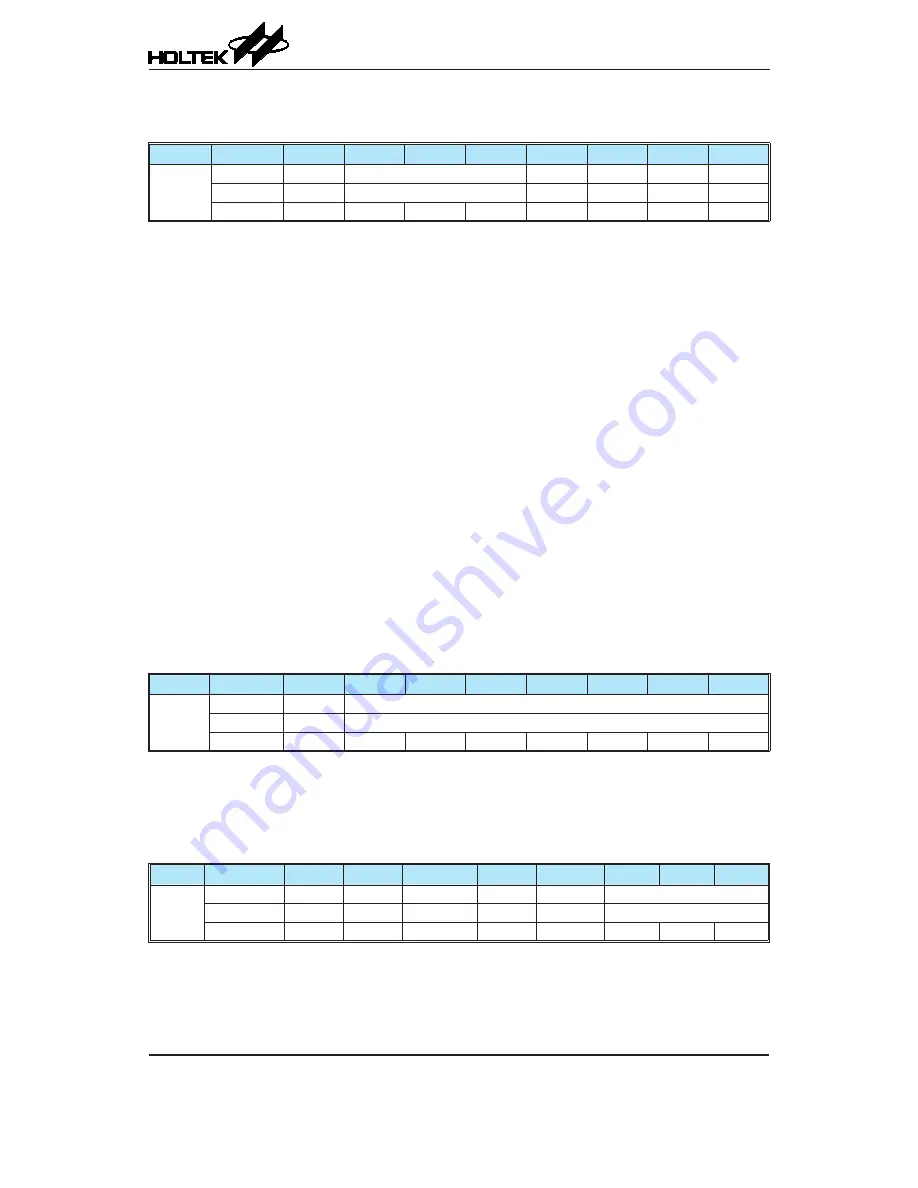

• PrimaryStatus Register

This register contains flags for indicating the status of modem, interrupt and FIFO.

Address

Bit

7

6

5

4

3

2

1

0

0x03

Name

—

ModemState[2:0]

IRQ

ERR

HiAlert

LoAlert

Type

—

R

R

R

R

R

Reset Value

—

0

0

0

0

1

0

1

Bit 7

Unimplemented, read as “0”

Bit 6~4

ModemState[2:0]

: Indicate the state of RX, TX and FIFO

000: Idle – No operation, neither the transmitter nor the receiver is in operation

001: TxSOF – The transmitter is transmitting “Start of Frame” pattern

010: TxData – The transmitter is transmitting data from FIFO or CRC

011: TxEOF – The transmitter is transmitting “End of Frame” pattern

100: RxPrepare – Receiver circuitry is initialized at this state and wait for time period defined by the

RxWait and BitPhase bits before starting to receive data

101: RxAwaiting – The receiver starts and is waiting for RX Start of Frame from tag

110: Receiving – The receiver is receiving data

Bit 3

IRQ

: Interrupt request indication

If there are one or more interrupt requests in InterruptFlag register, the IRQ flag will be set to 1.

Bit 2

ERR

: Error indication

If one or more errors occur in the Error register (Sector0-0x0A), the ERR flag will be set to 1.

Bit 1

HiAlert

: FIFO HiAlert warning flag

If FIFOLength ≥ 64-Waterlevel, the HiAlert flag will be set to 1.

Bit 0

LoAlert

: FIFO LoAlert warning flag

If FIFOLength ≤ Waterlevel, the LoAlert flag will be set to 1.

• FIFOLength Register

This register indicates the number of data remaining in the FIFO buffer.

Address

Bit

7

6

5

4

3

2

1

0

0x04

Name

—

FIFOLength[6:0]

Type

—

R

Reset Value

—

0

0

0

0

0

0

0

Bit 7

Unimplement, read as “0”

Bit 6~0

FIFOLength[6:0]

: Indicates the number of data remaining in the FIFO buffer

• SecondaryStatus Register

This register contains the status flags and values related to timers, CRC and receiver status.

Address

Bit

7

6

5

4

3

2

1

0

0x05

Name

Trunning RF_Det CRCReady EMD_Det SubC_Det

RxLastBit[2:0]

Type

R

R

R

R

R

R

Reset Value

0

0

1

0

0

0

0

0

Bit 7

Trunning

: Timer running state indication

If Timer is running, Trunning will be set to 1. The value in TimerValue register decreases at the rate of

timer clock, prescaling from 13.56MHz by TPreScaler bit field.