14 I

2

C (I2C)

14-16

Seiko Epson Corporation

S1C17M20/M21/M22/M23/M24/M25

TECHNICAL MANUAL (Rev. 1.0)

14.5 Interrupts

The I2C has a function to generate the interrupts shown in Table 14.5.1.

Table 14.5.1 I2C Interrupt Function

Interrupt

Interrupt flag

Set condition

Clear condition

End of data

transfer

I2CnINTF.BYTEENDIF When eight-bit data transfer and the following ACK/

NACK transfer are completed

Writing 1,

software reset

General call

address reception

I2CnINTF.GCIF

Slave mode only: When the general call address is

received

Writing 1,

software reset

NACK reception I2CnINTF.NACKIF

When a NACK is received

Writing 1,

software reset

STOP condition I2CnINTF. STOPIF

Master mode: When a STOP condition is gener-

ated and the bus free time (t

BUF

) between STOP and

START conditions has elapsed

Slave mode: When a STOP condition is detected

while the I2C Ch.n is selected as the slave currently

accessed

Writing 1,

software reset

START condition I2CnINTF. STARTIF

Master mode: When a START condition is issued

Slave mode: When an address match is detected

(including general call)

Writing 1,

software reset

Error detection

I2CnINTF. ERRIF

Refer to “Error Detection.”

Writing 1,

software reset

Receive buffer full I2CnINTF. RBFIF

When received data is loaded to the receive data

buffer

Reading received

data (to empty the

receive data buffer),

software reset

Transmit buffer

empty

I2CnINTF. TBEIF

Master mode: When a START condition is issued or

when an ACK is received from the slave

Slave mode: When transmit data written to the

transmit data buffer is transferred to the shift regis-

ter or when an address match is detected with R/W

bit set to 1

Writing transmit data

The I2C provides interrupt enable bits corresponding to each interrupt flag. An interrupt request is sent to the inter-

rupt controller only when the interrupt flag, of which interrupt has been enabled by the interrupt enable bit, is set.

For more information on interrupt control, refer to the “Interrupt Controller” chapter.

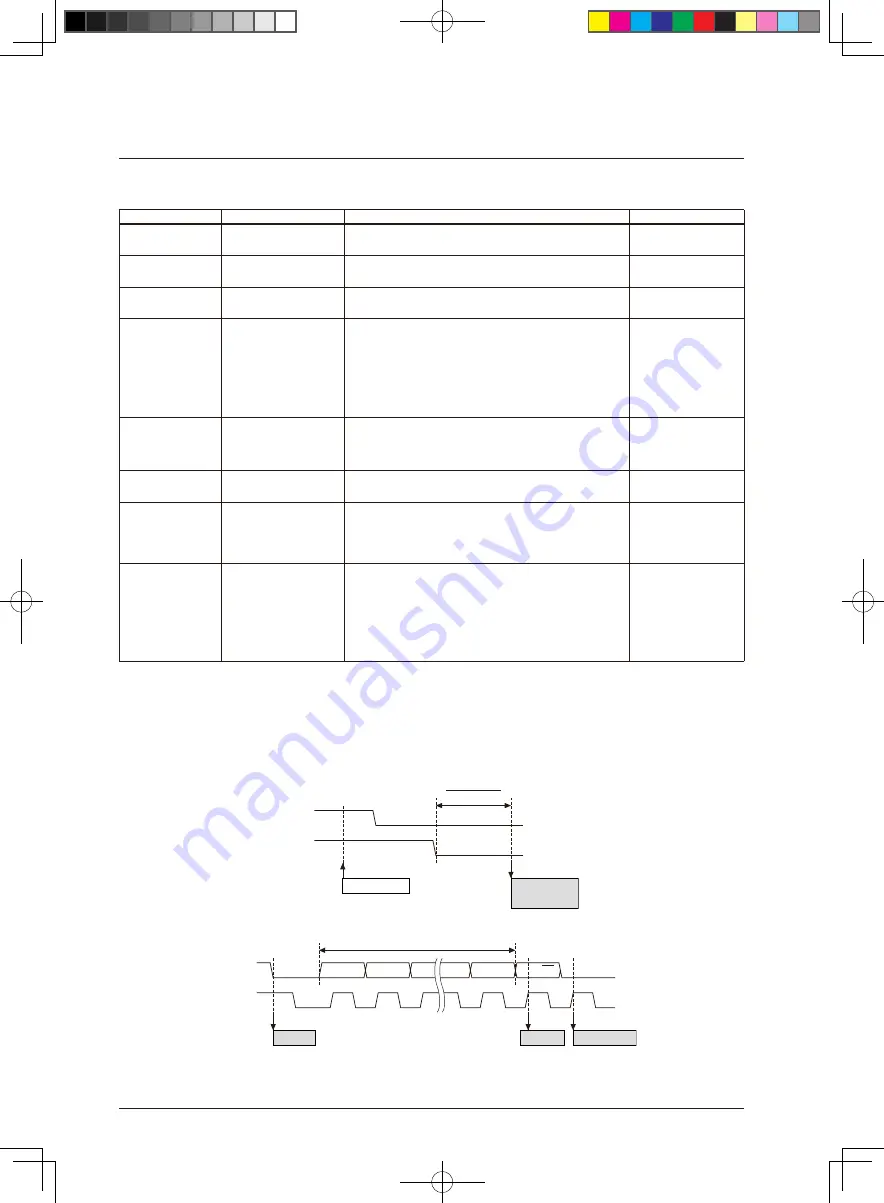

(1) START condition interrupt

Master mode

SDA

SCL

BRT + 3

f

CLK_I2Cn

TXSTART = 0

STARTIF = 1

TXSTART = 1

Slave mode

Address matching the I2CnOADR register

SDA

SCL

1

2

7

8

R/W

ACK

9

TR = 0/1 STARTIF = 1

BSY = 1