19 12-BIT A/D CONVERTER (ADC12A)

S1C17M20/M21/M22/M23/M24/M25

Seiko Epson Corporation

19-7

TECHNICAL MANUAL (Rev. 1.0)

Bit 10

BSYSTAT

This bit indicates whether the ADC12A is executing A/D conversion or not.

1 (R/W): A/D converting

0 (R/W): Idle

Bits 9–2

Reserved

Bit 1

ADST

This bit starts A/D conversion or enables to accept triggers.

1 (R/W): Start sampling and conversion (software trigger)/

Enable trigger acceptance (external trigger, 16-bit timer underflow trigger)

0 (R/W): Terminate conversion

This bit does not revert to 0 automatically after A/D conversion has completed. Write 0 to this bit once

and write 1 again to start another A/D conversion. After 0 is written to this bit to forcefully terminate

conversion, the ADC12A stops after the A/D conversion being executed is completed. Therefore, this

bit cannot be used to determine whether the ADC12A is executing A/D conversion or not.

Note

: The data written to the ADC12_

n

CTL.ADST bit must be retained for one or more CLK_T16_

k

clock cycles when 1 is written or two or more CLK_T16_

k

clock cycles when 0 is written.

Bit 0

MODEN

This bit enables the ADC12A operations.

1 (R/W): Enable ADC12A operations (The operating clock is supplied.)

0 (R/W): Disable ADC12A operations (The operating clock is stopped.)

Note

: After 0 is written to the ADC12_

n

CTL.MODEN bit, the ADC12A executes a terminate

processing. Before the clock source is deactivated, read the ADC12_

n

CTL.MODEN bit to

make sure that it is set to 0.

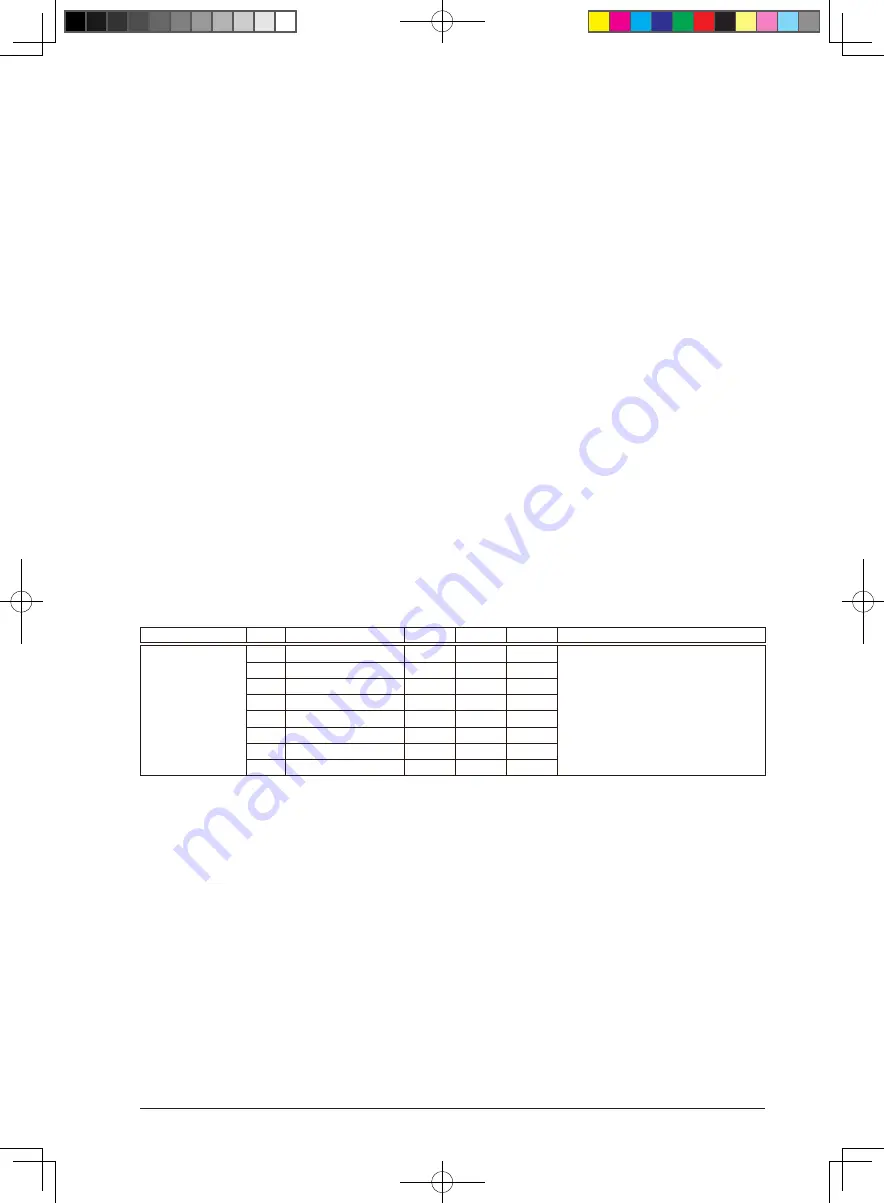

ADC12A Ch.

n

Trigger/Analog Input Select Register

Register name

Bit

Bit name

Initial

Reset

R/W

Remarks

ADC12_nTRG

15–14 –

0x0

–

R

–

13–11 ENDAIN[2:0]

0x0

H0

R/W

10–8 STAAIN[2:0]

0x0

H0

R/W

7

STMD

0

H0

R/W

6

CNVMD

0

H0

R/W

5–4 CNVTRG[1:0]

0x0

H0

R/W

3

–

0

–

R

2–0 SMPCLK[2:0]

0x7

H0

R/W

Note: Make sure that the ADC12_nCTL.BSYSTAT bit is set to 0 before altering the ADC12_nTRG register.

Bits 15–14 Reserved

Bits 13–11 ENDAIN[2:0]

These bits set the analog input pin to be A/D converted last.

See Table 19.6.1 for the relationship between analog input pins and bit setting values.

Note

: The analog input pin range to perform A/D conversion must be set as ADC12_

n

TRG.

ENDAIN[2:0] bits

≥

ADC12_

n

TRG.STAAIN[2:0] bits.

Bits 10–8 STAAIN[2:0]

These bits set the analog input pin to be A/D converted first.

See Table 19.6.1 for the relationship between analog input pins and bit setting values.