15 16-BIT PWM TIMERS (T16B)

S1C17M20/M21/M22/M23/M24/M25

Seiko Epson Corporation

15-15

TECHNICAL MANUAL (Rev. 1.0)

Counter

Trigger signal

0xffff

0x0000

T16BnCCCTLm.CAPTRG[1:0] bits = 0x3 (Trigger: falling and rising edges)

An overwrite error occurs as the T16BnINTF.CMPCAPmIF bit has not been cleared.

Time

Captured value

(T16BnCCRm register)

RUN = 1

CC[15:0]

→

Data (R)

CMPCAPmIF = 1

CMPCAPmIF = 1

Counter value

→

CC[15:0] Counter value

→

CC[15:0]

Counter value

→

CC[15:0]

CMPCAPmIF = 1

CAPOWmIF = 1

CC[15:0]

→

Data (R)

CMPCAPmIF = 0

MODEN = 1

PRESET = 1

Software operation

Hardware operation

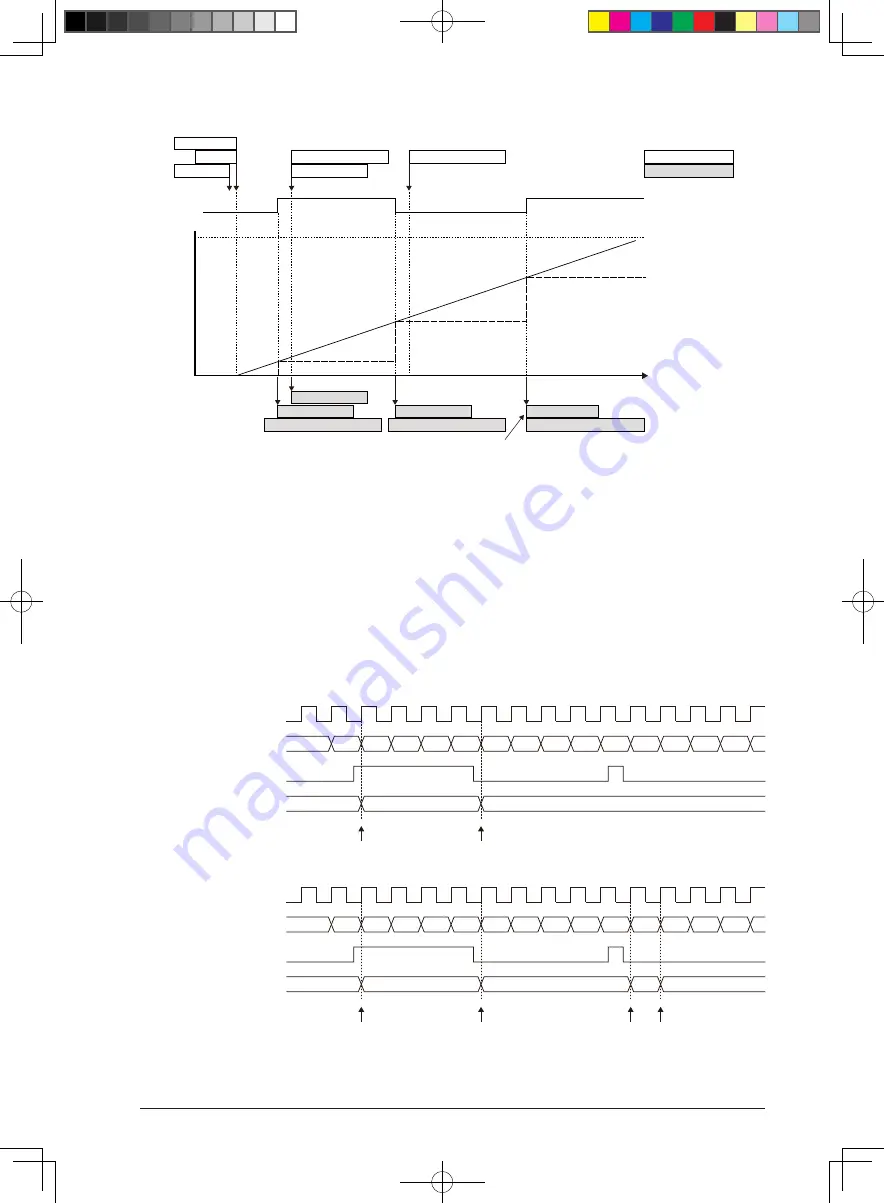

Figure 15.4.3.3 Operations in Capture Mode (Example in One-shot Up Count Mode)

Synchronous capture mode/asynchronous capture mode

The capture circuit can operate in two operating modes: synchronous capture mode and asynchronous cap-

ture mode.

Synchronous capture mode is provided to avoid the possibility of invalid data reading by capturing counter

data simultaneously with the counter being counted up/down. Set the T16B

n

CCCTL

m

.SCS bit to 1 to set

the capture circuit to synchronous capture mode. This mode captures counter data by synchronizing the

capture signal with the counter clock.

On the other hand, asynchronous capture mode can capture counter data by detecting a trigger pulse even if

the pulse is shorter than the counter clock cycle that becomes invalid in synchronous capture mode. Set the

T16B

n

CCCTL

m

.SCS bit to 0 to set the capture circuit to asynchronous capture mode.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

0

Count clock

T16BnTC.TC[15:0]

Capture trigger signal

T16BnCCRm.CC[15:0]

Capturing operation

(When T16BnCCCTLm.CAPTRG[1:0] bits = 0x3)

(1) Synchronous capture mode

1

5

Count clock

T16BnTC.TC[15:0]

Capture trigger signal

T16BnCCRm.CC[15:0]

Capturing operation

1

2

3

4

5

6

7

8

9

10

11

12

13

14

0

(When T16BnCCCTLm.CAPTRG[1:0] bits = 0x3)

(2) Asynchronous capture mode

1

5

10

11

Figure 15.4.3.4 Synchronous Capture Mode/Asynchronous Capture Mode