14 I

2

C (I2C)

S1C17M20/M21/M22/M23/M24/M25

Seiko Epson Corporation

14-13

TECHNICAL MANUAL (Rev. 1.0)

Receiving subsequent data

When the received data is read out from the I2C

n

RXD register after the I2C

n

INTF.RBFIF bit has been set to 1,

the I2C Ch.

n

clears the I2C

n

INTF.RBFIF bit to 0, releases SCL, and receives subsequent data sent from the

external master. After eight-bit data has been received, the I2C Ch.

n

sends an ACK and pulls down SCL to

low. The received data in the shift register is transferred to the receive data buffer and the I2C

n

INTF.RBFIF

and I2C

n

INTF.BYTEENDIF bits are both set to 1.

To return a NACK after eight-bit data is received, such as when terminating data reception, write 1 to the

I2C

n

CTL.TXNACK bit before the data reception is completed. The I2C

n

CTL.TXNACK bit is automati-

cally cleared to 0 after a NACK has been sent.

STOP/repeated START condition detection

It is the same as the data transmission in slave mode.

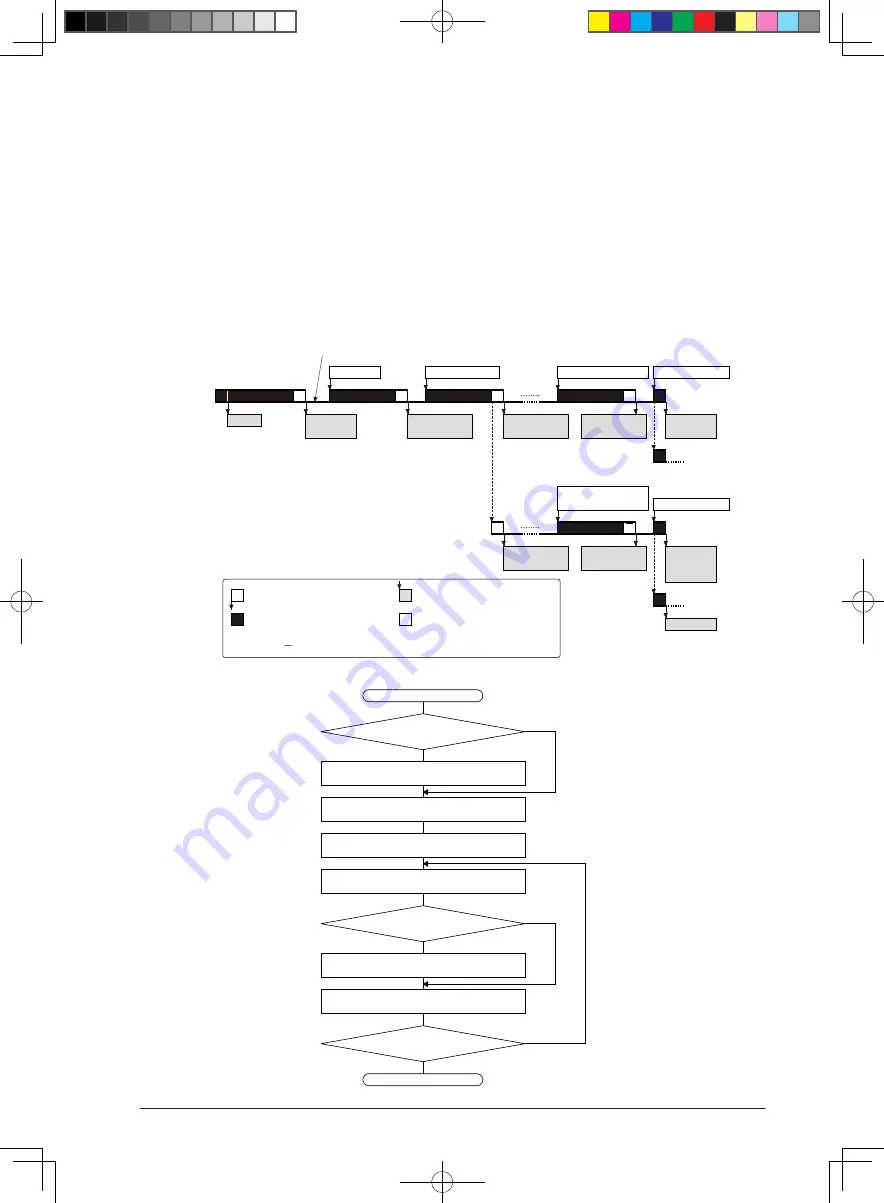

S

P

Sr

A

STARTIF = 1

BSY = 0

STOPIF = 1

Saddr/W

A

Data 1

A

Data 2

A

Data N

A

RXD[7:0]

→

Data 1

RXD[7:0]

→

Data (N -1) RXD[7:0]

→

Data N

RBFIF = 1

BYTEENDIF = 1

RBFIF = 1

BYTEENDIF = 1

RBFIF = 1

BYTEENDIF = 1

P

Sr

A

Data N

TXNACK = 1

RXD[7:0]

→

Data (N -1) RXD[7:0]

→

Data N

RBFIF = 1

BYTEENDIF = 1

RBFIF = 1

BYTEENDIF = 1

I

2

C bus

Clock stretching by I2C

Software bit operations

Operations by the external master

S: START condition, Sr: Repeated START condition, P: STOP condition,

A: ACK, A: NACK, Saddr/W: Slave a W(0), Data n: 8-bit data

Hardware bit operations

Operations by I2C (slave mode)

BSY = 0

TXNACK = 0

STOPIF = 1

TR = 0

STARTIF = 1

BSY = 1

TXNACK = 0

Figure 14.4.6.1 Example of Data Receiving Operations in Slave Mode

Data reception

Write 1 to the I2CnCTL.TXNACK bit

YES

One-byte reception?

End

Wait for an interrupt request

(I2CnINTF.STARTIF = 1)

YES

NO

NO

Last data received?

Write 1 to the I2CnINTF.STARTIF bit

Wait for an interrupt request

(I2CnINTF.RBFIF = 1)

Write 1 to the I2CnCTL.TXNACK bit

Last data received next?

Read receive data from the I2CnRXD register

YES

NO

Figure 14.4.6.2 Slave Mode Data Reception Flowchart