Application Note

9 of 42

001-65209 Rev.*I

2021-03-19

Getting Started with FX2LP™

FX2LP Introduction

PC[7:0]/GPIFADR[7:0]

PE7/GPIFADR8

PE6/T2EX

PE5/INT6

PE4/RxD1OUT

PE3/RxD0OUT

PE2/T2OUT

PE1/T1OUT

PE0/T0OUT

CTL[5:3]

RDY[5:2]

TxD1

RxD0

TxD0

RxD1

T1

INT4

INT5#

T2

WR#

T0

RD#

EA

CS#

OE#

PSEN#

A[15:0]

D[7:0]

100

128

PD[7:0]

PB[7:0]

RDY0

RDY1

CTL0

CTL1

CTL2

XTALIN

XTALOUT

DPLUS

DMINUS

SCL

SDA

RESET#

WAKEUP#

XCLK

CLKOUT

INT0#/PA0

PA1/DA0

PA2

WU2/PA3

PA4

PA5

PA6

PA7

56

IORDY

DMARQ

IOW

IOR

DMACK

←INTRQ

→DA0

→DA1

→DA2

→CS0

→CS1

→DASP

→RESET

FIFO Data

GPIF

SLRD

SLWR

PRGFLAG

INFULL

OUTEMPTY

←INT0

←INT1

←SLOE

PA3

←FIFOADR0

←FIFOADR1

←PKTEND

PA7

FIFO Data

Slave FIFO

Single Chip

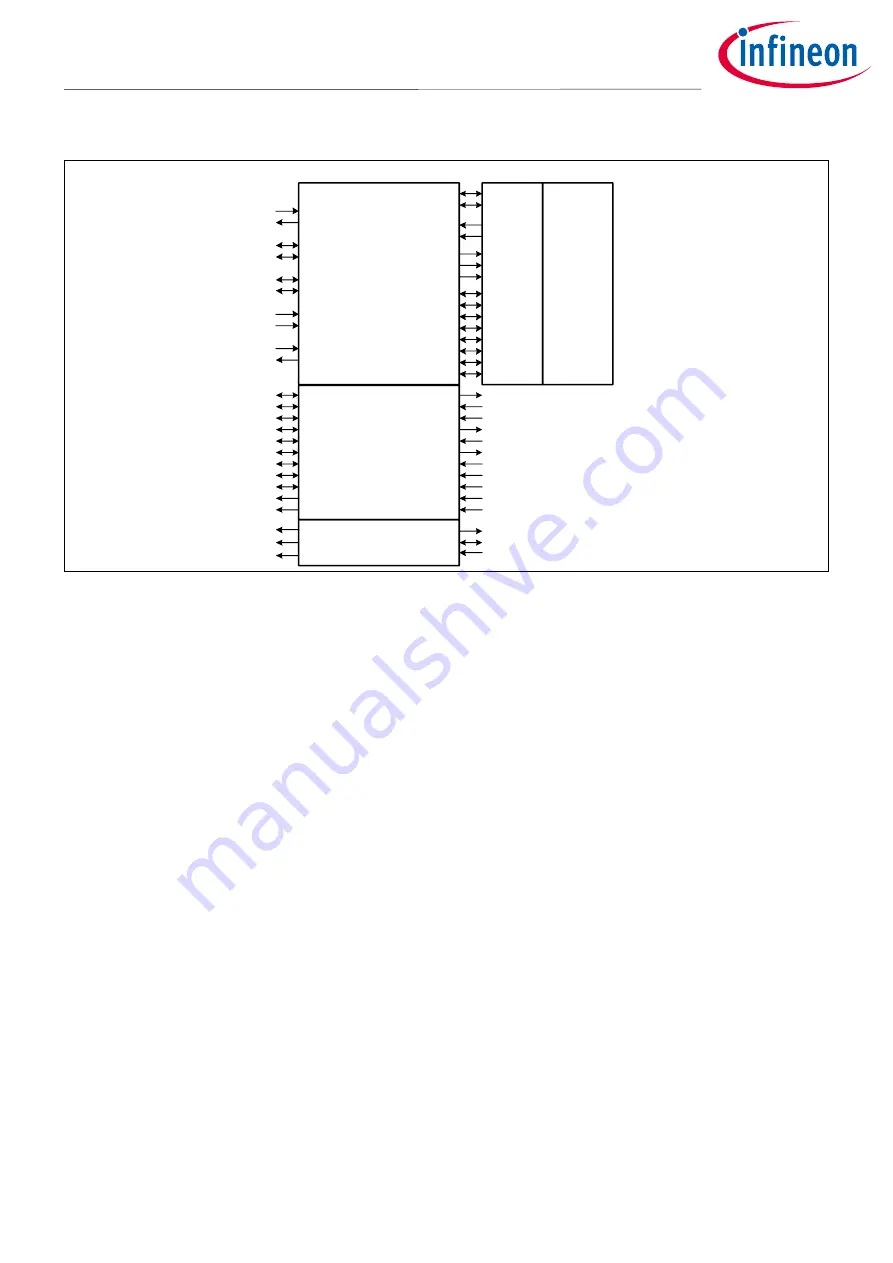

Figure 5

Three FX2LP Package Choices

The 56-pin package is the lowest-cost version of FX2LP. The signals on the left edge of the 56-pin block (in

are common to all package versions in the family. Three modes are available in all package versions:

single-chip, GPIF, and Slave FIFO. These modes define the signals shown on the right edge of the 56-pin block

(in

). The 8051 selects the interface mode using an internal register. Single-chip mode is the power-on

default configuration.

The 100-pin package adds functionality to the 56-pin package by adding 44 pins:

•

Two additional 8-bit I/O ports, PORTC and PORTE.

•

Seven additional GPIF controls (CTL) and ready (RDY) signals.

•

Nine non-multiplexed control signals (two UARTs, three timer inputs, INT4, and INT5#).

•

Eight additional control signals multiplexed on to PORTE.

•

Nine GPIF address lines, multiplexed on to PORTC(8) and PORTE(1),

•

RD# and WR# signals, which may be used as read and write strobes for PORTC.

The 128-pin package adds 8051 address and data buses and their control signals. These added pins allow

FX2LP to operate with an external 8051 memory. This package is used in the FX2LP Development Board.