Application Note

5 of 42

001-65209 Rev.*I

2021-03-19

Getting Started with FX2LP™

FX2LP Introduction

3

FX2LP Introduction

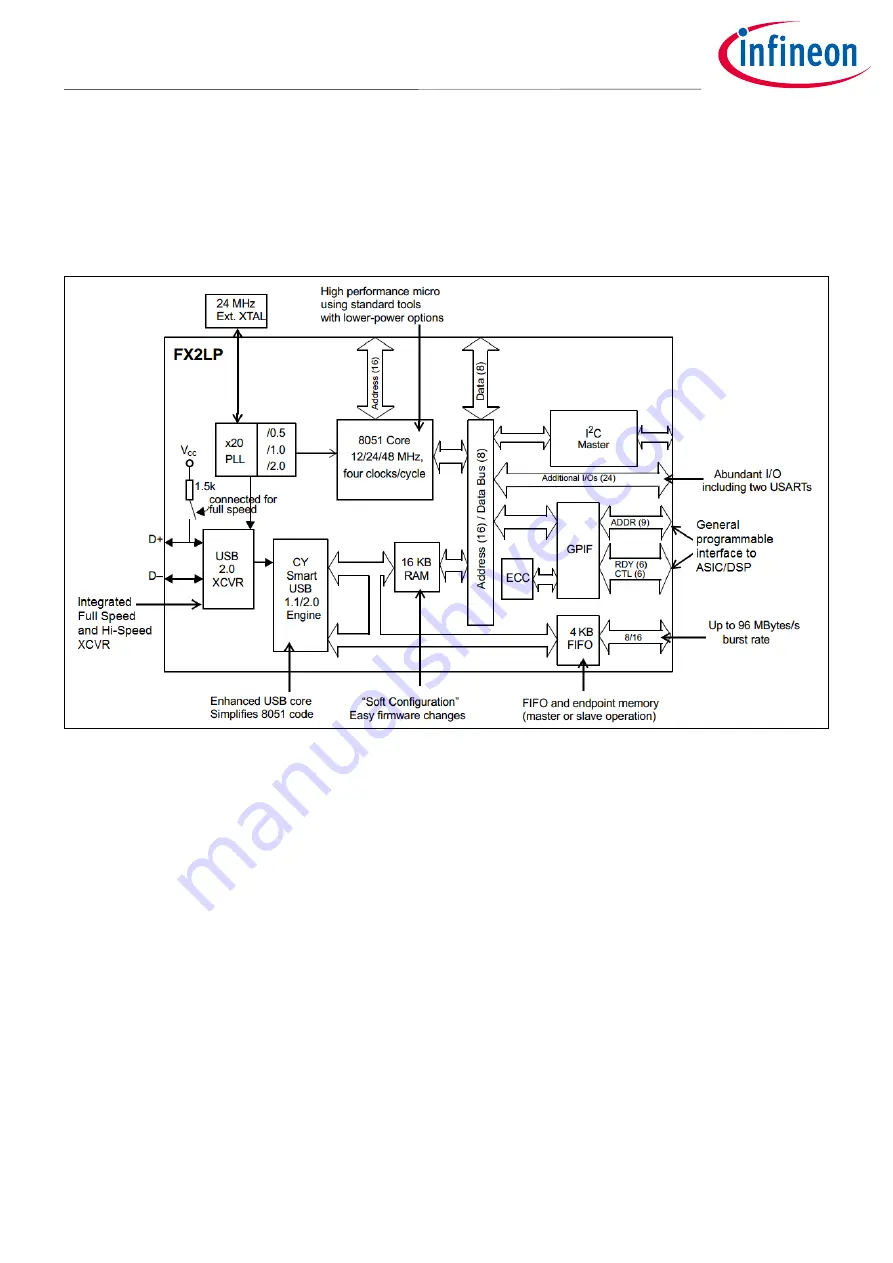

FX2LP integrates a USB 2.0 transceiver, a smart serial interface engine (SIE), large data buffers, an enhanced

8051 microcontroller, and a programmable peripheral interface in a single chip. A simplified FX2LP block

diagram is shown in

Figure 1

FX2LP Block Diagram

The function of FX2LP is to transfer data between a USB host and a peripheral device. FX2LP provides this

connectivity using parallel and serial interfaces. In systems where the FX2LP CPU is not required to modify the

data before sending it to the USB host, the FX2LP firmware only needs to initialize its hardware transfer units,

allowing high-bandwidth USB transfers to proceed without CPU intervention.

FX2LP can be programmed to enumerate as any USB device type, conforming to a standard USB class, such as

HID or mass storage, or a custom device.

3.1

FX2LP Features

This section briefly describes the key features of FX2LP.

3.1.1

USB Interface

Hi-Speed USB transfers can be visualized as supporting two ends of a pipe. On one end, the pipe receives and

sends data at 480 Mbps over the USB interface, as shown in

The other end of the pipe is described in