WM8940

22

Rev 4.4

INPUT PGA VOLUME CONTROL

The input microphone PGA has a gain range from -12dB to +35.25dB in 0.75dB steps. The gain from

the MICN input to the PGA output and from the AUX amplifier to the PGA output are always common

and controlled by the register bits INPPGAVOL[5:0]. These register bits also affect the MICP pin

when MICP2INPPGA=1.

When the Automatic Level Control (ALC) is enabled the input PGA gain is then controlled

automatically and the INPPGAVOL bits should not be used.

REGISTER

ADDRESS

BIT

LABEL

DEFAULT

DESCRIPTION

R45

Input PGA

volume

control

7

INPPGAZC

0

Input PGA zero cross enable:

0=Update gain when gain register changes

1=Update gain on 1

st

zero cross after gain

register write.

6

INPPGAMUTE

1

Mute control for input PGA:

0=Input PGA not muted, normal operation

1=Input PGA muted (and disconnected from

the following input BOOST stage).

5:0

INPPGAVOL

010000

Input PGA volume

000000 = -12dB

000001 = -11.25db

.

010000 = 0dB

.

111111 = 35.25dB

R32

ALC control 1

8

ALCSEL

0

ALC function select:

0=ALC off (PGA gain set by INPPGAVOL

register bits)

1=ALC on (ALC controls PGA gain)

Table 4 Input PGA Volume Control

AUXILIARY INPUT

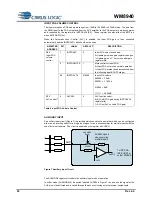

An auxiliary input circuit (Figure 7) is provided which consists of an amplifier which can be configured

either as an inverting buffer for a single input signal or as a mixer/summer for multiple inputs with the

use of external resistors. The circuit is enabled by the register bit AUXEN.

-

+

VMID

AUX

20k

20k

AUXSW closed

when summing

multiple inputs

To INP PGA,

INP BOOST or

output MIXERS

AUXMODE

R44[3]

AUXSW

AUXOP

Figure 7 Auxiliary Input Circuit

The AUXMODE register bit controls the auxiliary input mode of operation:

In buffer mode (AUXMODE=0) the switch labelled AUXSW in Figure 7 is open and the signal at the

AUX pin will be buffered and inverted through the aux circuit using only the internal components.