ADM-

XP

User Manual

ADM-XR-IIPro User Manual

Page 7 of 29

Version 0.2

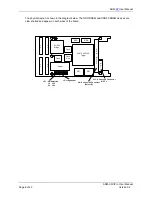

3 Hardware

Overview

The XP is based on the architecture of the ADM-XRC-II with changes to accommodate the enhanced

resources and needs of the Virtex-II PRO device.

The XP follows the architecture of the ADM-XRC series and decouples the “target” FPGA from the “bridge”

device to allow the entire target to be available for user applications. This ensures the user can be up and

running with the minimum of effort and without the complexity of PCI design.

The bridge includes local bus control and monitoring together with flexible configuration options for the bridge

and the target device.

The bridge is capable of 66MHz PCI or PCI-X operation with 64-bit or 32-bit operation. The local bus supports

64-bit at upto 80Mhz

The target FPGA is a Virtex-II-PRO device incorporating FPGA fabric, multi-gigabit transceivers and two

PowerPC cores.

DDR SDRAM, ZBT and flash memory connect to the target FPGA and are supported by Xilinx or third party IP.

IO functionality is provided using XRM modules connecting to the 180 pin SAMTEC QSE and 28 pin SAMTEC

QSE DP connectors.

Virtex II FG676

2V1500

Alpha Data PCI/

PCIX to Local Bus

Bridge

Virtex II Pro - FF1704

2VP70-2VP125

SSRAM

Target

Config

Flash

Clocks

Power

JTAG

Local Bus

SSRAM

64/66 PCI

PCIX 133

146 Bit

IO Bus

MGT Bus

IO Connector/

headers

PN4 IO

DDR2

SDRAM

Target

User

Flash

Bridge

Config

Flash

Config

Control

CPLD

SSRAM

SSRAM

DDR2

SDRAM