ADM-

XP

User Manual

ADM-XR-IIPro User Manual

Page 13 of 29

Version 0.2

5.4 DDR2

SSRAM

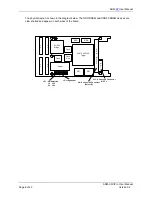

The XP supports four independent banks of CIO DDR2 SSRAM memory. The devices fitted are Samsung

512K *36 (K7I163684-FC16) parts or a functional equivalent. As an upgrade option 1Mx36 (K7I323684-FC16)

devices can also be fitted.

2VP70 / 2VP100

FF1704

Bank 6

VCCO=1.8V

DDR2

SSRAM

Add0[0:21]

Dq0[0:31]

DDR2 SSRAM Bank 0

Bank 7

VCCO=1.8V

Bwe0[0:3]

Cclk0/Cclkb0

Kclk0/Kclkb0

DDR2

SSRAM

Add0[0:21]

Dq0[0:31]

Bwe0[0:3]

Cclk0/Cclkb0

Kclk0/Kclkb0

DDR2

SSRAM

Add1[0:21]

Dq1[0:31]

Bwe1[0:3]

Cclk1/Cclkb1

Kclk1/Kclkb1

DDR2

SSRAM

Add0[0:21]

Dq0[0:31]

Bwe0[0:3]

Cclk0/Cclkb0

Kclk0/Kclkb0

DDR2 SSRAM Bank1

DDR2 SSRAM Bank 2

DDR2 SSRAM Bank 3

The pins required for each SSRAM controller bank are listed below.

Name

FPGA Pin Type

Description

ZBTx_ad[0:21] Output Address

bus

ZBTx_dq[0:31] Bidir

Data

bus

ZBTx_rw

Output

Read(1) / Write(0)

ZBTx_bwe{0..3]

Output

Byte enables for writes

ZBTx_nld

Output

Initiates a transaction

ZBTx_Cclk/ZBTx_nCclk

Output

SSRAM Output Data Clock

ZBTx_Kclk/ZBTx_nKclk Output

SSRAM Clock for Inputs

ZBTx_DOFF Output

SSRAM

DLL

Enable

The SSRAM pins should be configured for HSTL_II_18 operation

The SSRAM clock Cclks and Kclks are intended to be used with clock-forwarding implemented in a DDR IOB

with a DCM used to adjust for SSRAM clock to output delays on the data input path to the FPGA.